5G技术如何影响芯片设计(深度)

边缘计算兴起,让计算在靠近数据的边缘完成成为可能,文章“如何在端上高效地部署AI模型”,将详细介绍如何在边缘部署算法和应用。

据华为预测,到 2025年,5G将为全球 58% 的人口提供服务,而中国将成为全球最大的 5G 市场。5G 及其管理机构 3GPP 对于将 5G 能力扩展到移动市场之外的领域抱有极高期望。的确,5G 在流媒体视频、社交媒体等方面大大提高了手机的速度,但5G 也为进入许多新领域开辟了道路。其中包括低功耗物联网 (IoT) 应用,如资产跟踪、汽车与基础设施的自动连接、宽带互联网服务、有线电视服务等等。

然而,除基带处理器之外,5G 还会影响芯片设计。由于需要满足大量应用的需求,吞吐量显著提高,这对整个系统都有影响,并且会改变无数 SoC 的设计。这些 SoC包括必须容纳更高带宽和复杂通信能力的应用处理器。这些应用处理器可用于手机、AR/VR 耳机、无人机、摄像头、平板电脑、一体机以及许多其他消费类设备中。

除了消费类设备外,基础设施也必须能够满足这些消费类设备的高密度要求,并将传入的数据转发到适当的目的地。这可能是另一个网络、本地设备、云数据中心或本地数据中心,对于这些应用,边缘计算将是支持未来分布式计算的基本趋势。所有这些趋势都需要升级 SoC,满足 5G 覆盖范围要求,而不仅仅是基带处理器。

5G 半导体细分

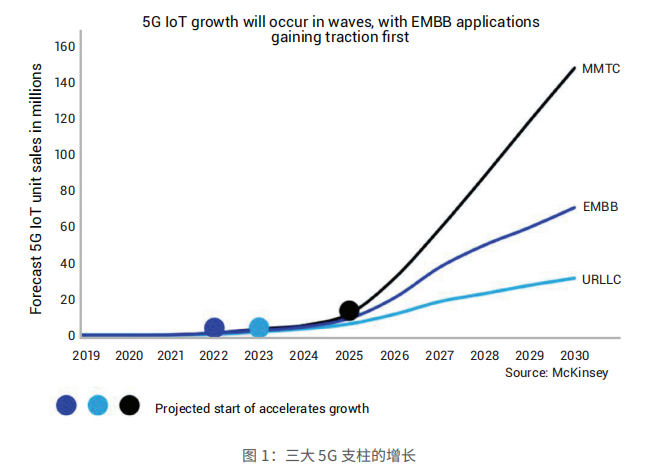

5G 的发展通常提到三大支柱:增强型移动宽带 (EMBB)、物联网和机器对机器通信 (MMTC),以及汽车和超可靠低延迟通信 (URLLC)。这三个领域的增长将以波浪的形式出现,其中 EMBB 应用作为明显。

移动宽带推动着当今手机中新型应用和基带处理器的发展,我们已经看到,厂商正在为如何提供这些服务展开竞赛。然而,与移动宽带相关的最显著的增长体现在支持这一需求的基础架构中。

多年来,关于微基站(室外)、微微基站(室内 / 室外)和毫微微基站(室内)的消息不绝于耳。借助 5G 和 mmWave 技术,室内小区和小小区的增长已成为半导体的主要关注点。这不仅仅指的是新型基带处理器。边缘计算的发展及其构想伴随着基础架构中的所有网络能力而出现,而且用于在本地管理和分析数据的服务器不断增加。5G 提供商已经制定了满足这些要求的宏伟计划,而且一些支持更低功耗和更低延迟的服务器 SoC 已经推出。

除了 5G 基础架构内的服务器 SoC 之外,市场还需要专门的 AI 加速器,用于分析大量数据,并提供更多有价值的服务来管理这些数据。

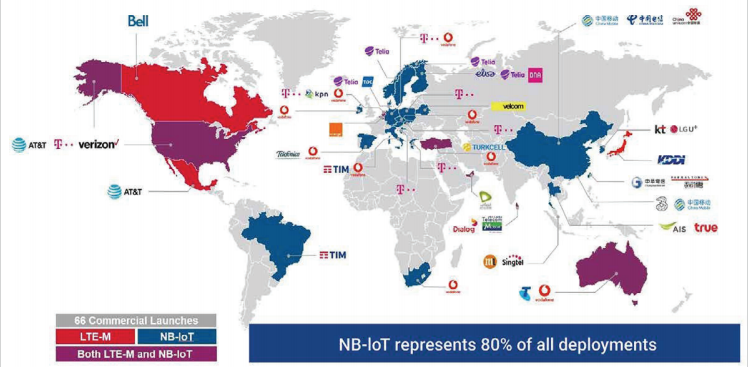

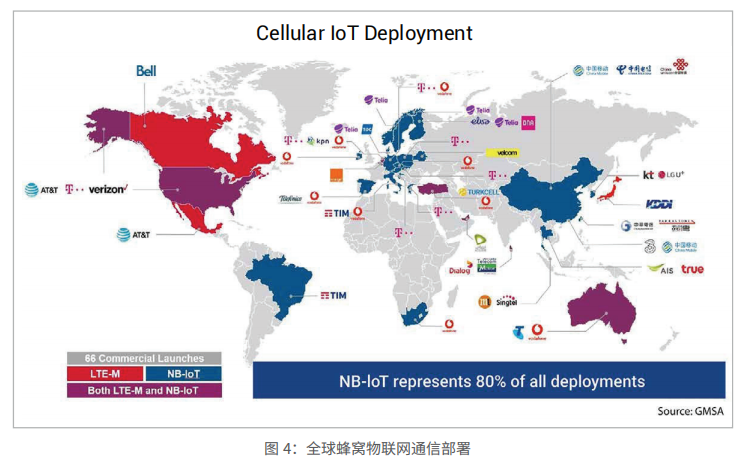

除了高带宽视频应用外,5G 还整合了 LTE-M 和 NB-IoT 等低功耗技术,以支持 5G 基础架构内的应用,例如资产跟踪、一键语音功能和定位服务。这些低功耗、最少数据节点的数量达到数十亿,使网络流量和能力大大增加。SoC 设计必须能够容纳新节点,以添加 LTE-M 和 NB-IoT,以及在基础架构中产生的流量。

除了高带宽和低功耗物联网应用之外,5G 还整合了用于关键任务和自动驾驶功能的低延迟、超可靠通信能力。这些领域推动着整个设计界不断探索技术和系统的极限。

推动5G发展的主要厂商

对于 5G 的实施,服务提供商倾向于在讨论中占主导地位。但是,这些服务提供商需要依靠技术领导者开发的申请专利的 5G 创新技术,包括爱立信、三星、高通、诺基亚、英特尔、华为、Qorvva、中兴通讯、Keysight 等。

5G实施的进展图

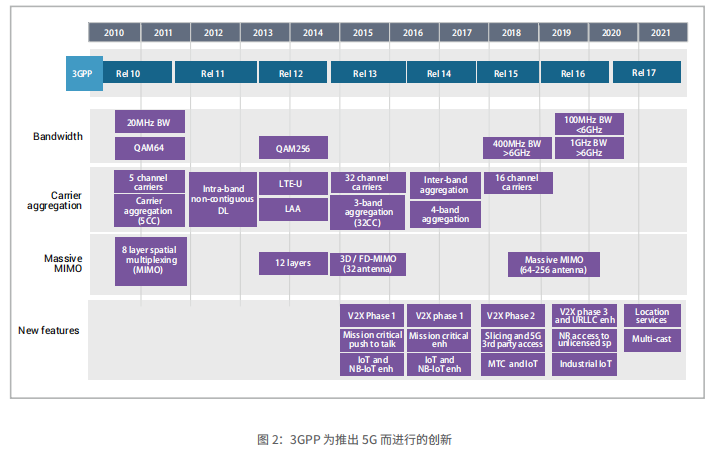

导致 5G 推出过程中每个 3GPP 版本的一些创新。三个关键因素推动着 10Gbps 无线连接目标的实现。这些因素包括提高带宽能力、增强载波聚合和大规模 MIMO(即更多具有波束成形能力的天线)。

带宽一直是讨论 5G 改进的核心话题,然而,延迟和功耗是实现 5G 宏伟目标必须克服的另外两个挑战。

带宽

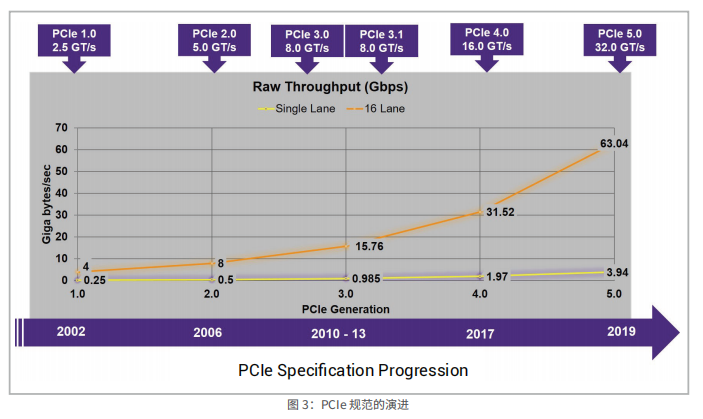

由于这是一种系统挑战,而不仅仅是无线技术挑战,因此,整个设备中的 SoC 设计带宽非常重要。高带宽、基于标准的 IP 是 5G SoC系统设计的关键部分。这首先从手机引入 LPDDR 开始,已从最初的 LPDDR4/4x 发展到如今的 LPDDR5。DDR5 目前在基础架构 5G网络和服务器 SoC 中广泛采用。MIPI 和 JEDEC 通过 MIPI CSI-2、MIPI I3C 以及 JEDEC UFS 3.0 引入了更高的带宽能力,以实现与移动传感器和存储器的连接。PCI Express (PCIe) 从 PCIe 3.0 快速升级到 PCIe 4.0 和 5.0,如图 3 所示。

以太网持续扩展带宽,而基础架构 SoC 正迅速迁移到 400G 和 800G,这需要包括 56G 和 112G 在内的最新高速 SerDes PHY。蓝牙升级了低能耗蓝牙,使蓝牙经典版本已经过时,因为蓝牙技术目前已开始支持音频能力。USB、消费类设备中的基本连接能力已从 3.0 升级到 3.1 和 3.2,而现在,USB4 已经推出。除了基于标准的 IP 外,用于处理自组织网络的 AI 处理器已经推出,而且用于满足日益复杂的基带处理要求而推出的高度并行矢量 DSP 处理器已在 SoC 中采用,用于满足 5G 载波聚合以及大规模 MIMO 处理和带宽需求。

延迟

以缩短延迟的需求举例,当前的 5G 规范期望往返延迟短于 1ms。在 2019 年秋季推出的未来 6G 计划预计往返延迟为 10 微秒。虽然这可能比 SoC 中的某些内存访问操作的延迟高出几个数量级,但在依然如此低的延迟下,SoC 设计中的每个时钟周期都更加重要。为了缩短 SoC 中的延迟,通过采用专家服务构建高度集成和优化的子系统而缩短延迟的趋势非常明显。此外,基于标准的新协议可缩短延迟,例如 Compute Express Link (CX)L。新思科技在为缩短延迟提供优化的系统方面是领导者,除紧密耦合的存储器之外,还包括行业领先的低延迟 DDR 控制器、延迟远低于最低规格的新型 CXL 控制器,以及消除总线结构并将寄存器直接映射到处理器的接口子系统。

功耗

为了扩展移动提供商的能力,为物联网提供服务,低功耗协议现已推出,例如 LTE-M 和 NB-IoT。这些协议需要新的处理解决方案、新的无线解决方案以及低功耗系统设计方法和 IP 能力,包括在接近阈值电压下运行、电压和频率缩放以及智能时钟门控。

5G 应用场景

5G 移动与基础架构5G 的目标是提供与当前有线家庭宽带解决方案相竞争的速度。为了做到这一点,3GPP 更新了多项规范,这些更新注重更高带宽、更多信道聚合和大规模天线阵列等方面的升级。为了适应这种高吞吐量,SoC 设计必须集成多个要素,包括复杂的基带处理、高速模拟 IP 和支持最新高速标准以及安全性的接口 IP。

5G SoC 离不开处理解决方案,用于有效处理基带解决方案所需的多种不同工作负载。具有信号处理能力并经过优化的处理器可以增加每个周期完成的工作量,从而减少这些复杂解决方案消耗的能源。这些架构需要最新的 VLIW DSP、并行矢量浮点和多核配置,以处理高级 5G 所要求的基带能力。对于复杂 FFT,对减少周期数进行基准测试也是实现 5G 非常重要的一点。

5G channel and carrier aggregation需要移动和基础架构需要高达 10Gbps 的数据传输速率,为了满足这一要求,下一代5G 芯片组中的模拟 IP 必须支持 GHz 信道带宽和 256QAM。5G 需要极高的速度(每秒千兆次采样 (GSPS))、支持多种调制 / 解调架构的高分辨率 RFADC 和 RFDAC,例如 Direct-RF 或更传统的 Zero-IF 和超外差实现。另外,可支持不同 MIMO 排列,并能够有效处理最大 5G 信道和载波聚合需求的 AFE 非常重要。

5G 物联网

为了将移动无线技术扩展到更多设备,3GPP 定义了更低带宽、简化的通信协议,例如 NB-IoT 和 LTE-M,以满足物联网的低功耗和低成本要求。低功耗基带处理对于无线物联网应用至关重要。

5G 汽车 (V2X)

5G 将支持极低延迟能力,使控件的反馈系统延迟短于 1ms。这需要依靠创新的 IP 解决方案来实现。汽车 SoC 是 3GPP 定义的低延迟要求的关键驱动要素。但是,汽车解决方案需要高质量、高可靠性和安全性,必须从一开始就经过验证,从而使 IP 成为成功的关键途径。

5G 对 SoC 的影响总结

5G 给下一代 SoC 带来了多方面的挑战,而不仅仅限于高带宽无线方面。这些挑战包括增加系统带宽,降低 SoC 延迟以及显著降低物联网的功耗。要将 5G 推向市场,在最重要的工艺技术节点使用基于标准的可信 IP 和经过验证的处理以及模拟 IP 必不可少。

推荐阅读:如何在端上高效地部署AI模型

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

推荐阅读

更多架构相关技术知识总结请参考“架构师全店铺技术资料打包”相关电子书(35本技术资料打包汇总详情可通过“阅读原文”获取)。

全店内容持续更新,现下单“全店铺技术资料打包(全)”,后续可享全店内容更新“免费”赠阅,价格仅收198元(原总价305元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“架构师技术全店资料打包汇总(全)”电子书资料详情。