PCIe5.0和CXL最大吞吐量和最低延时设计

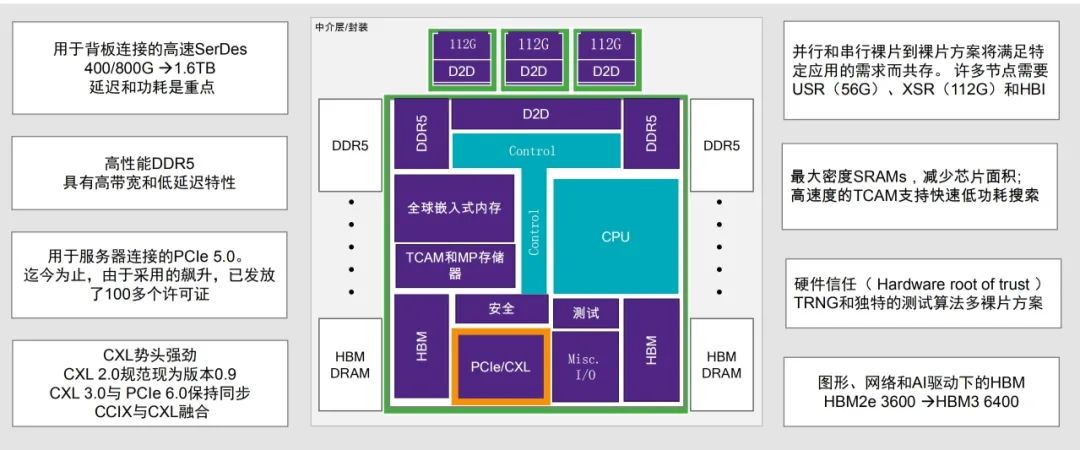

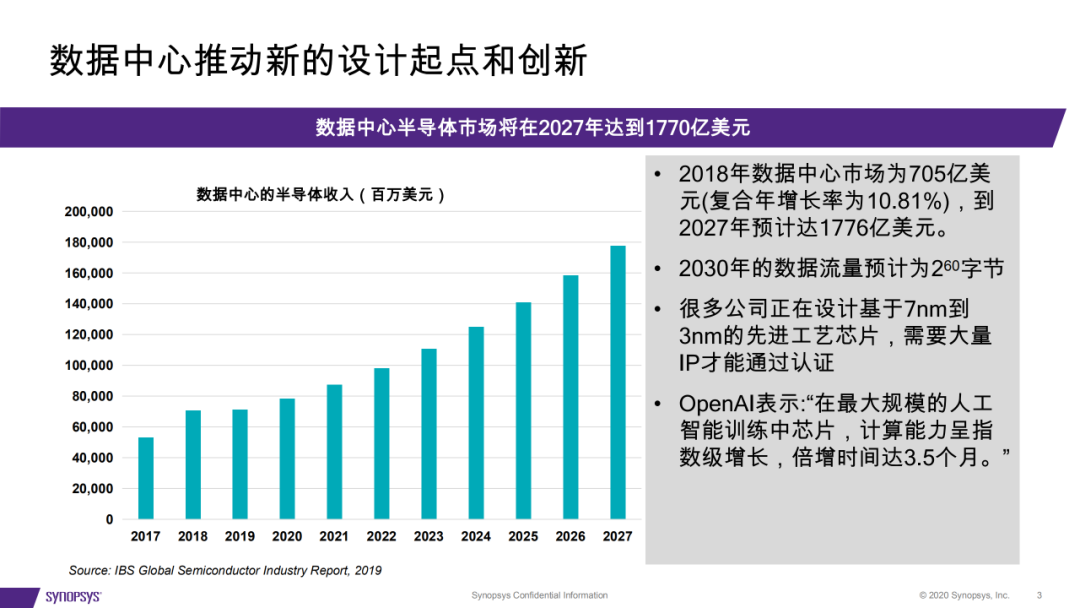

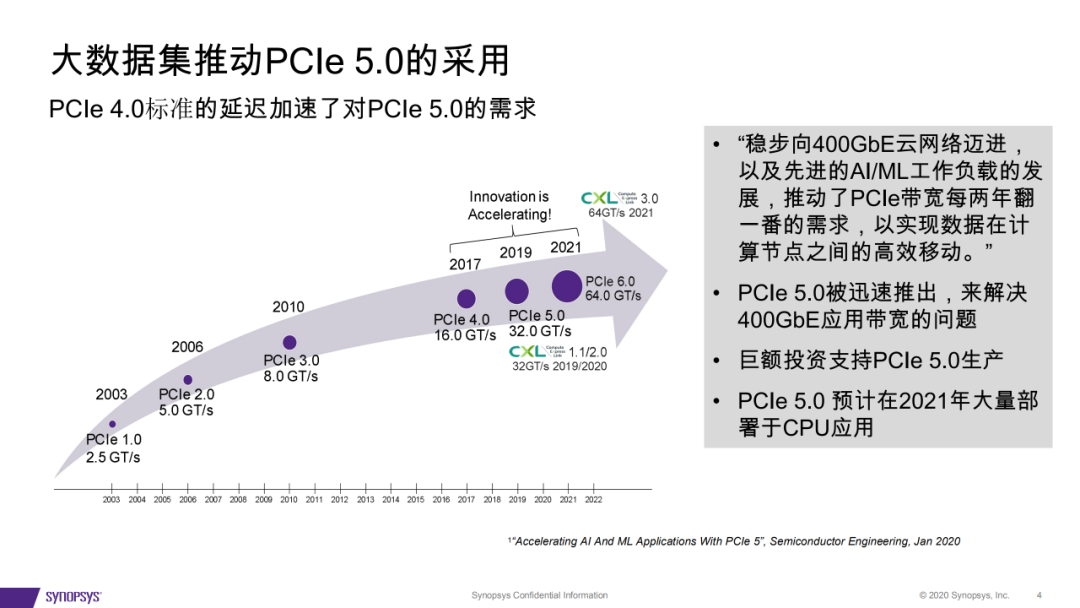

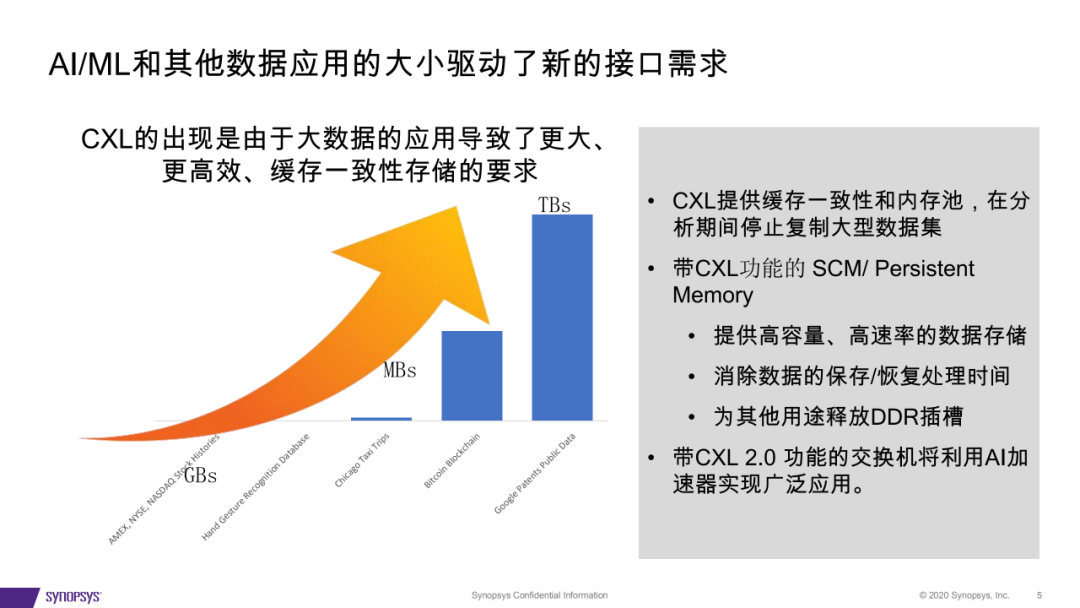

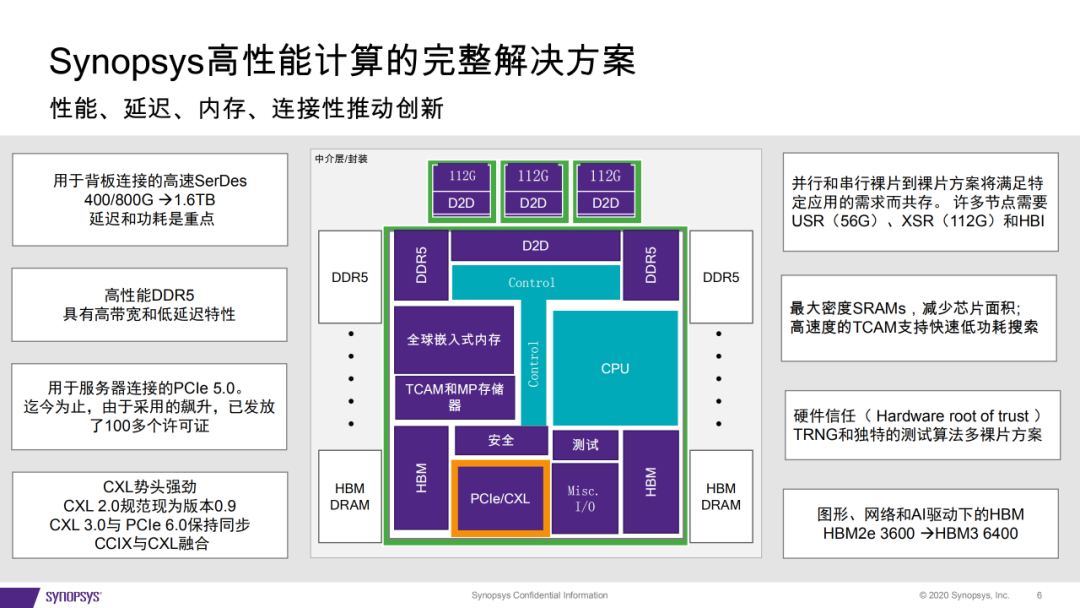

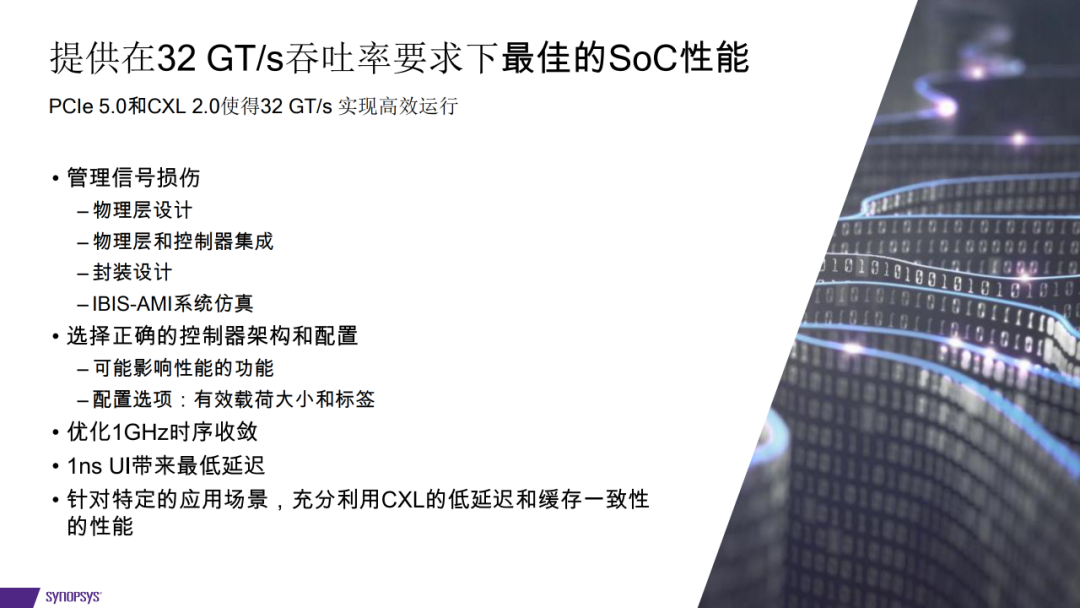

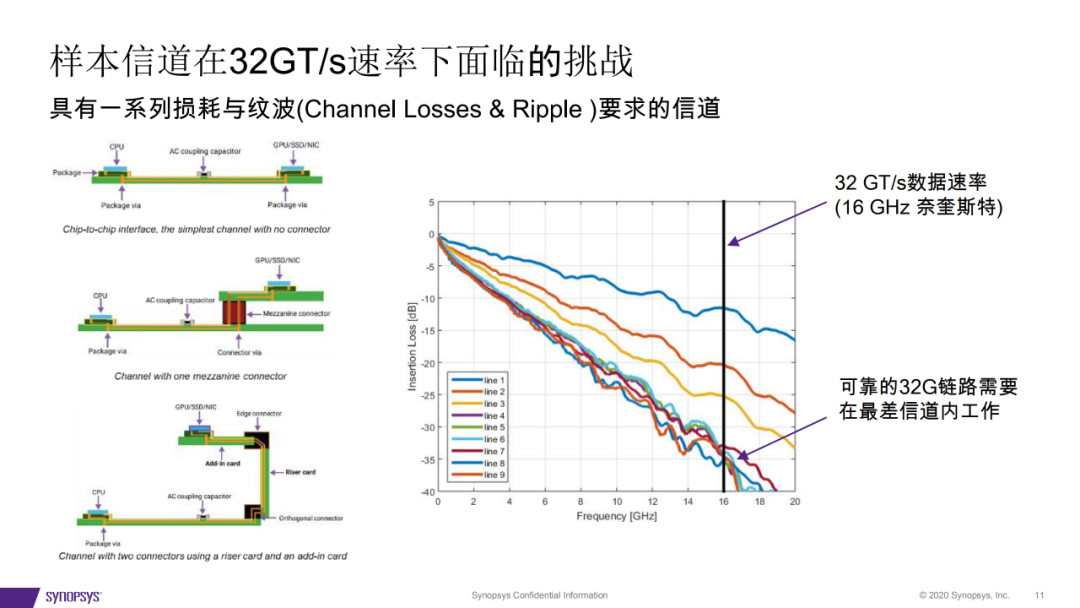

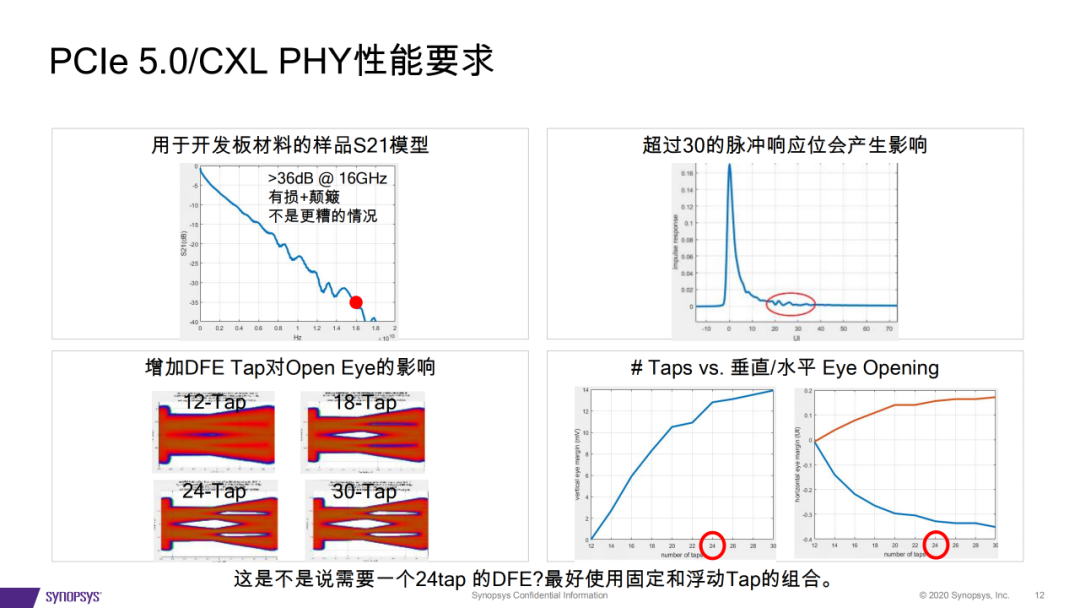

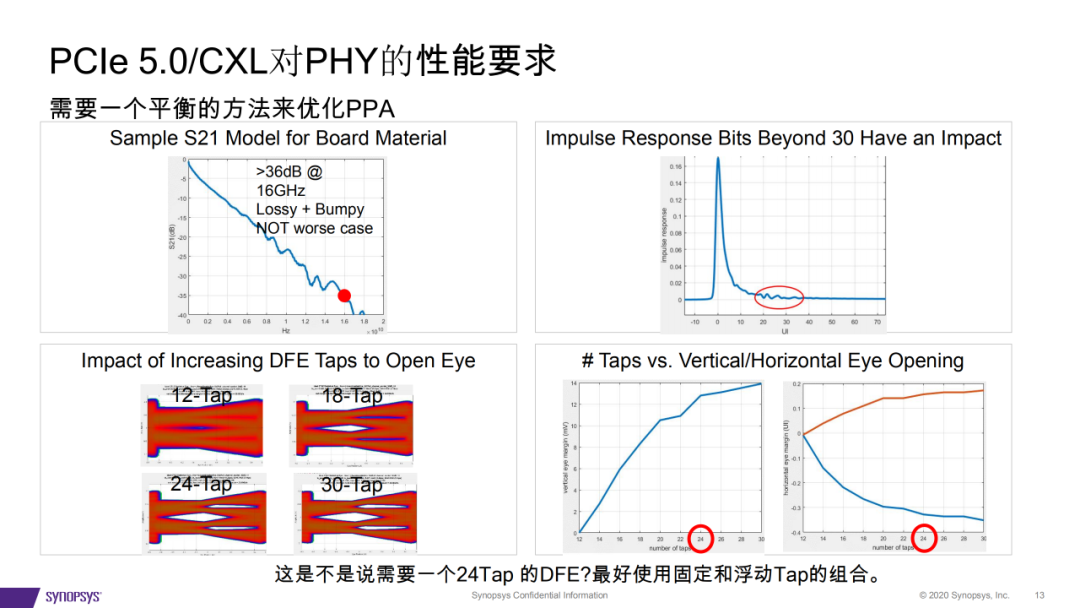

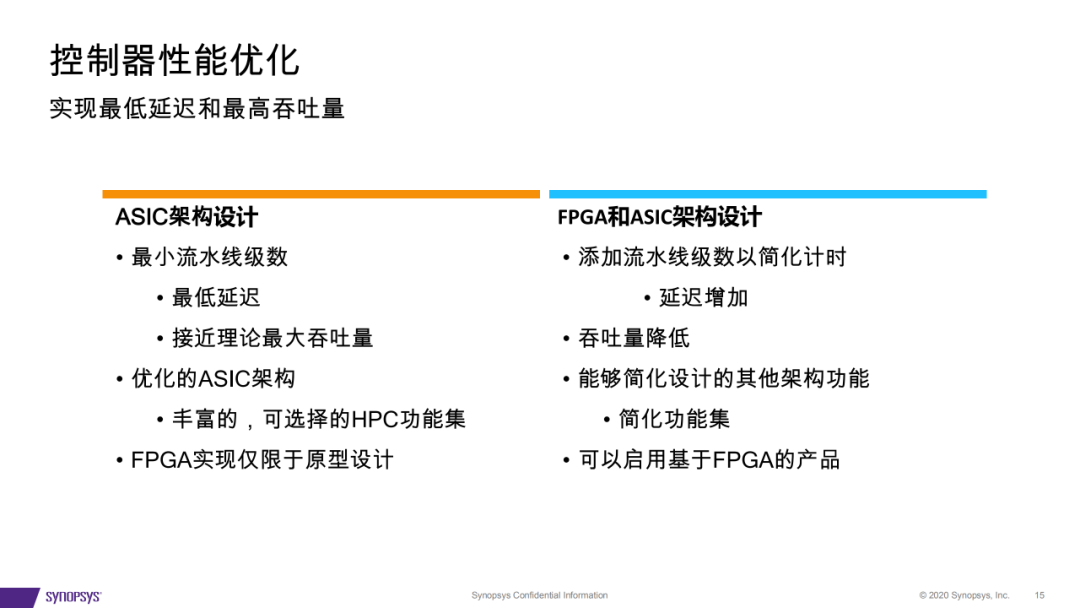

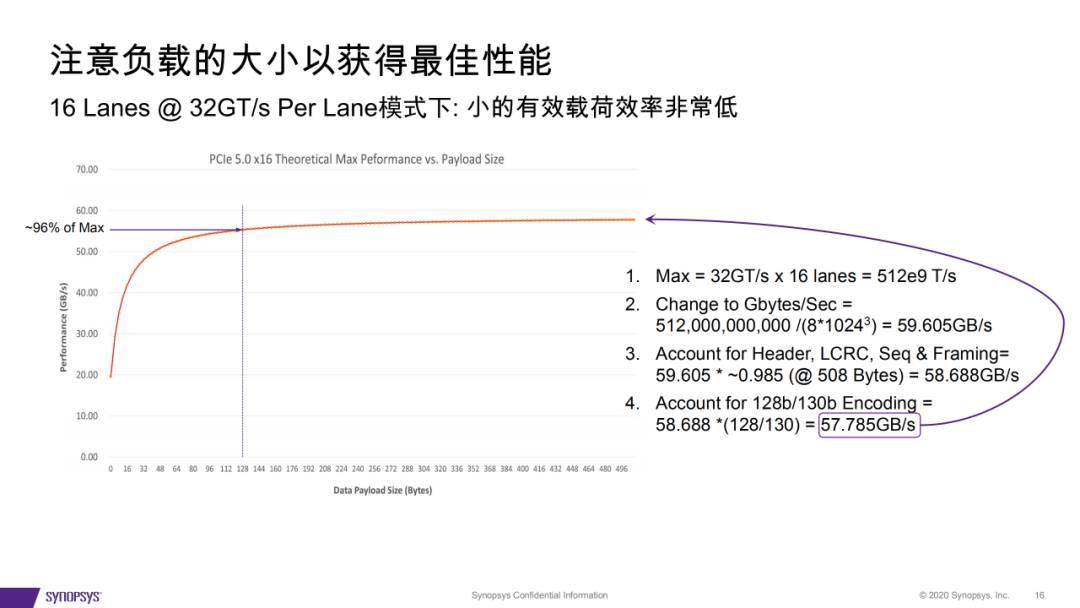

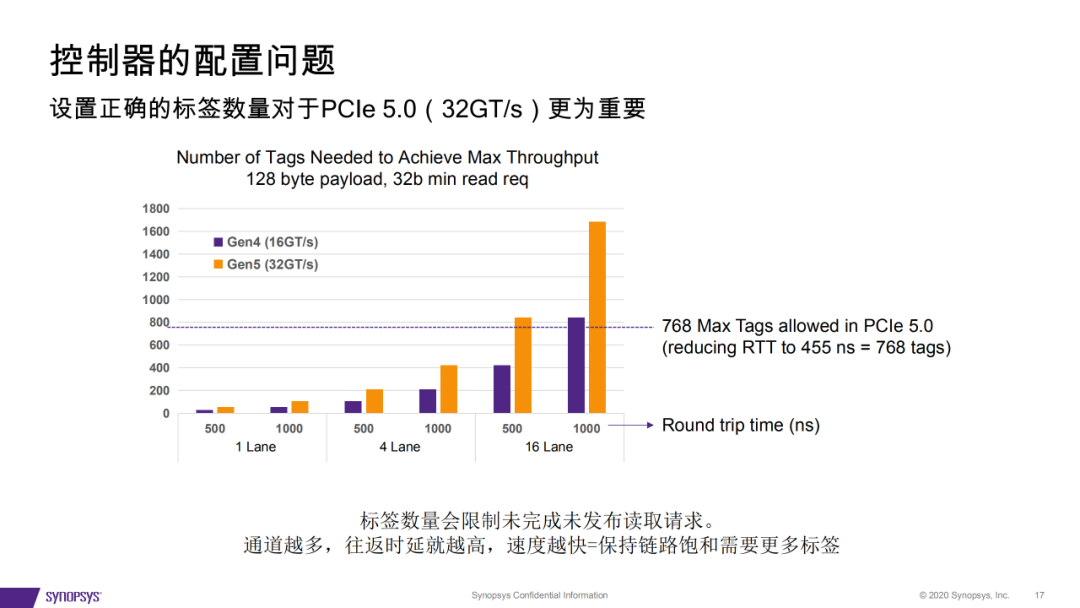

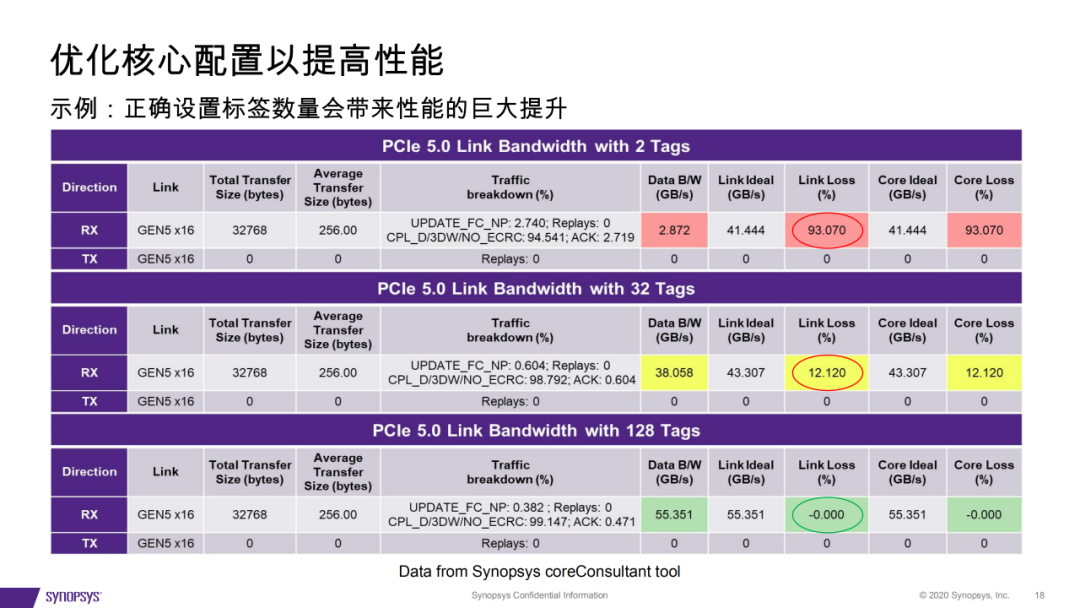

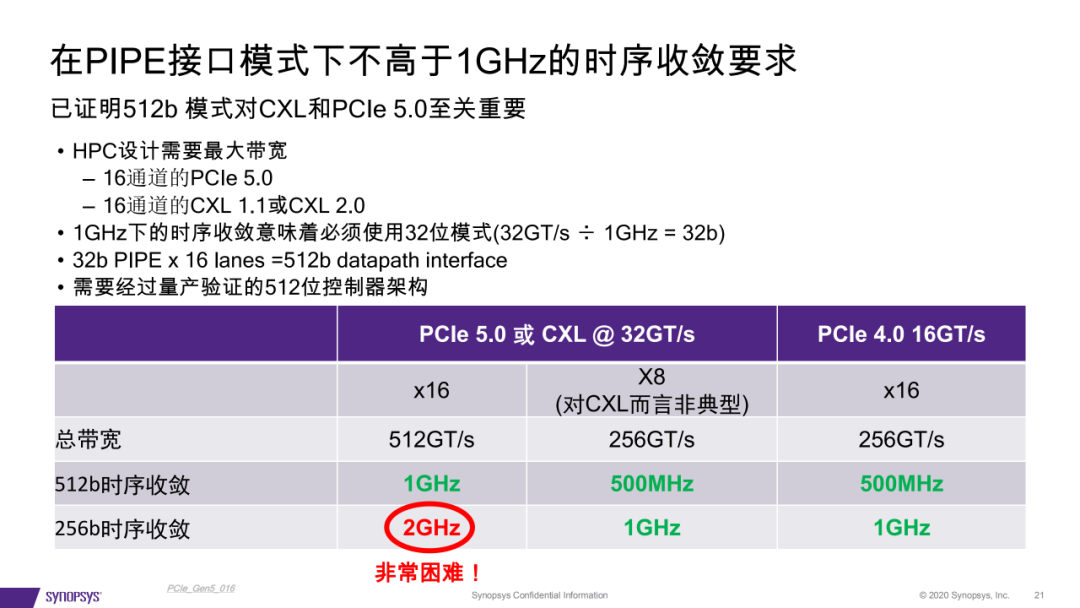

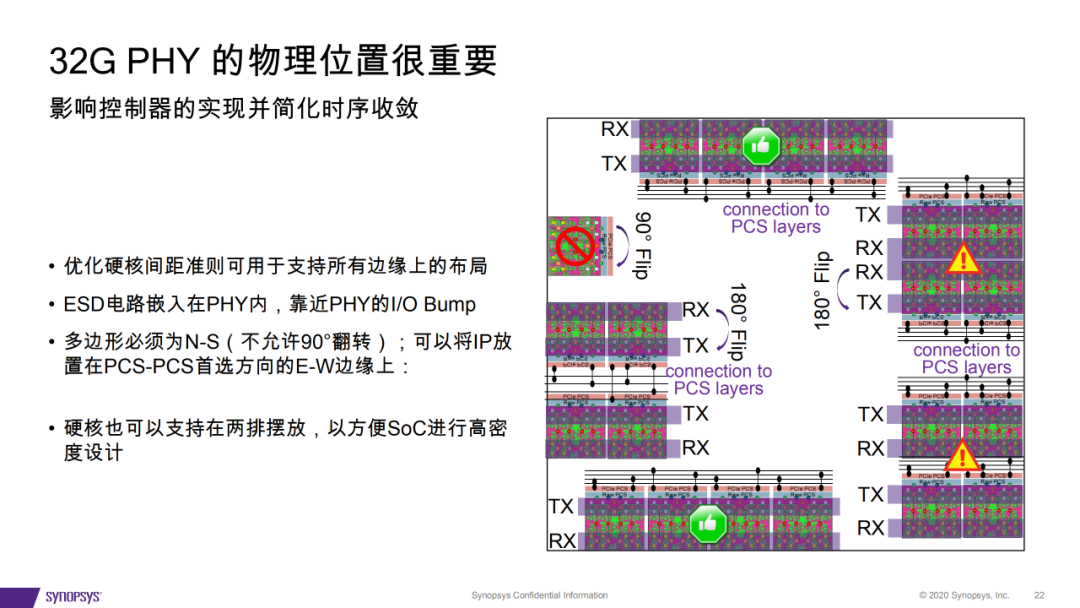

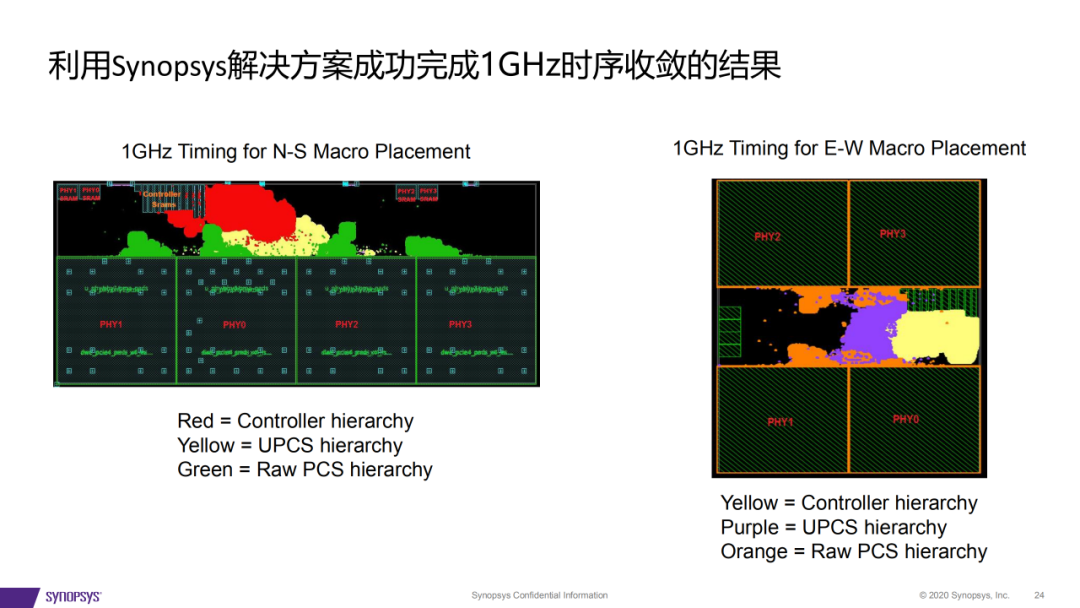

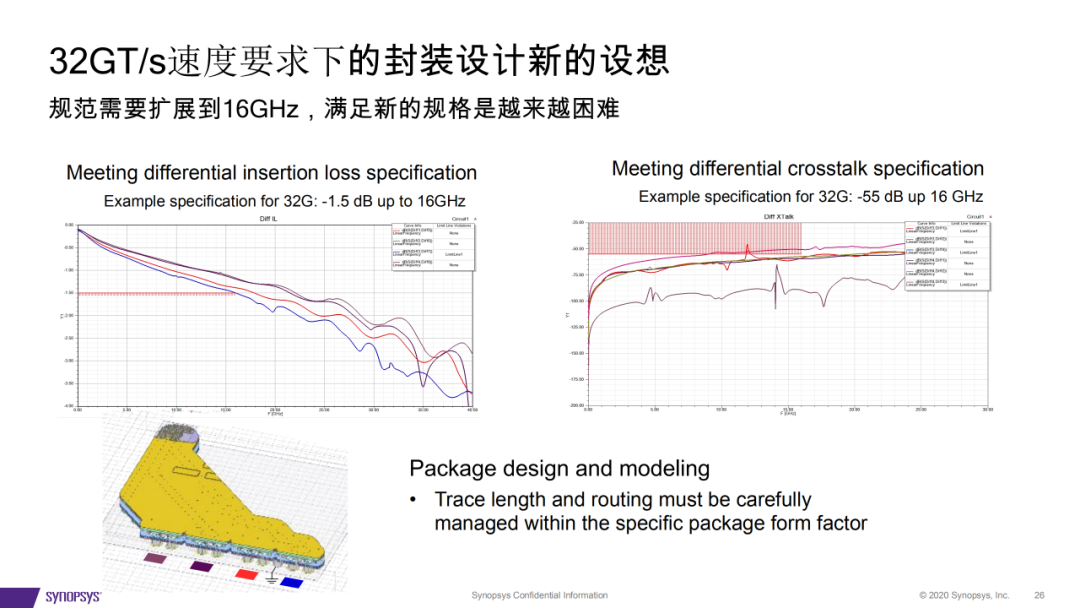

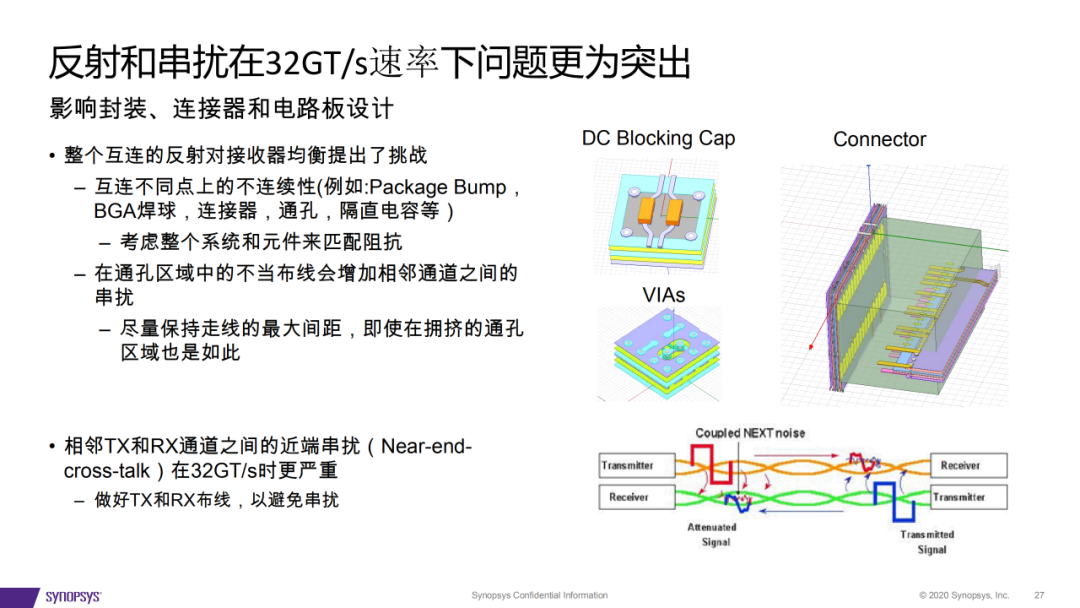

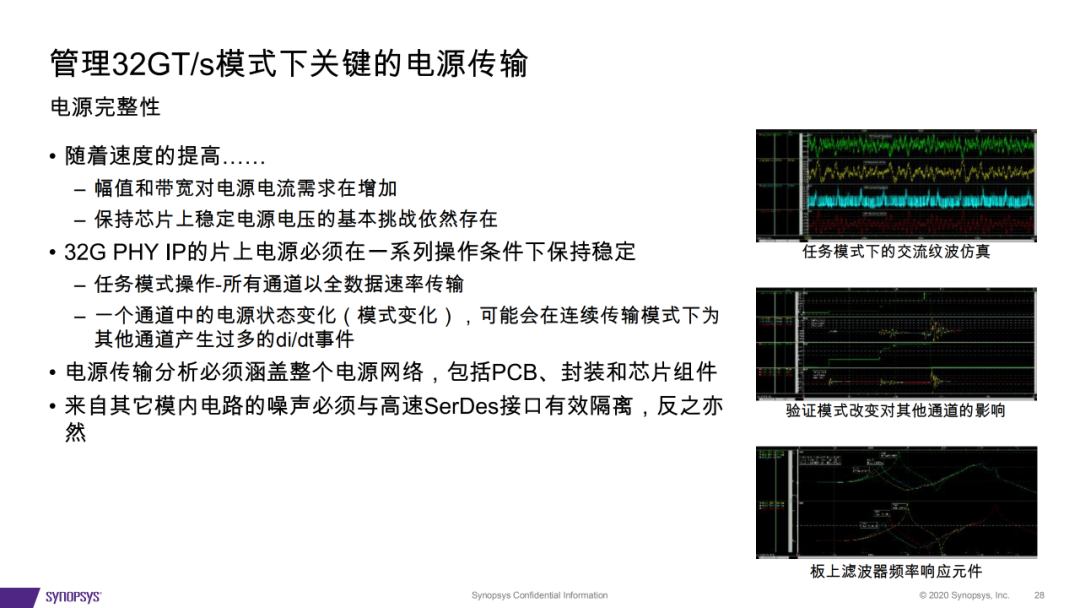

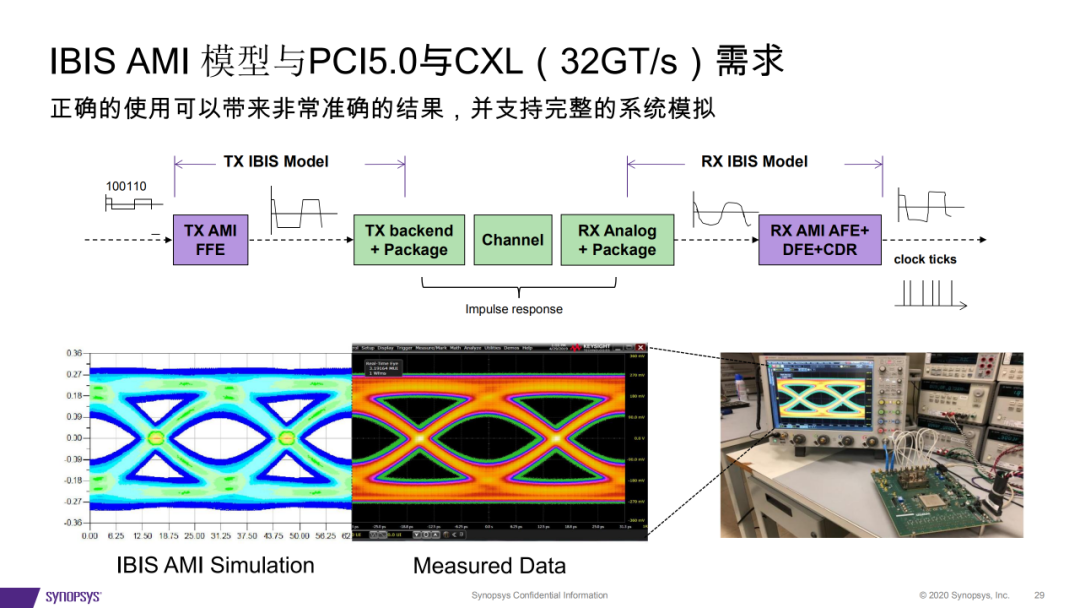

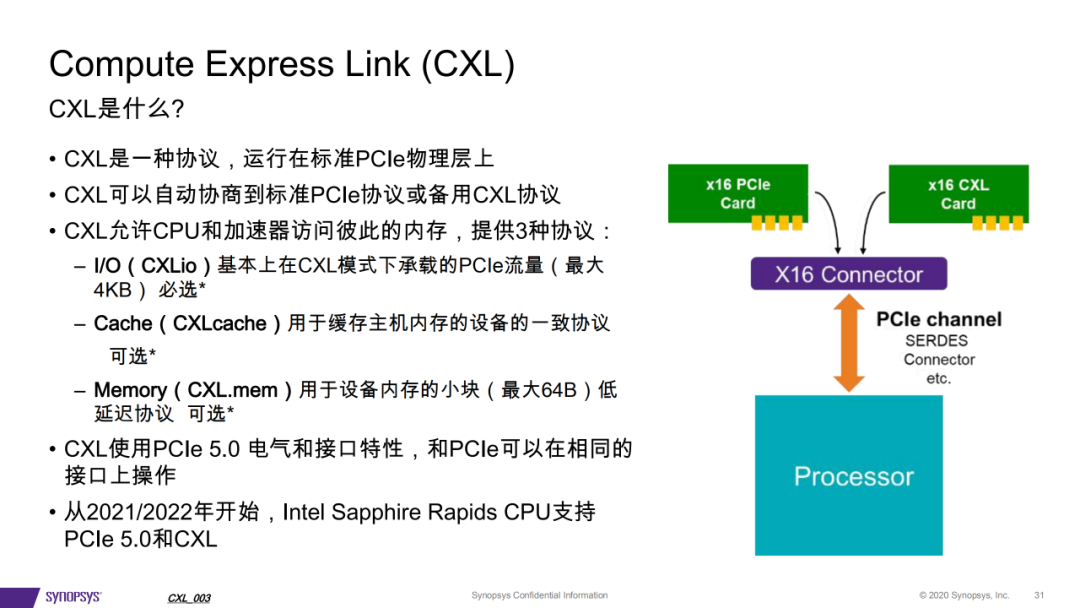

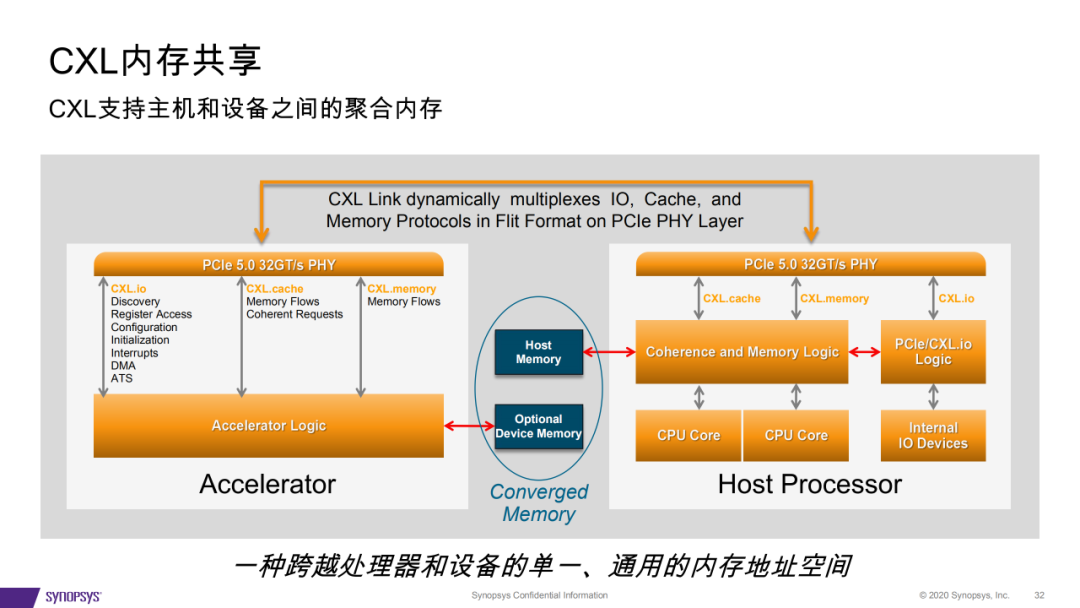

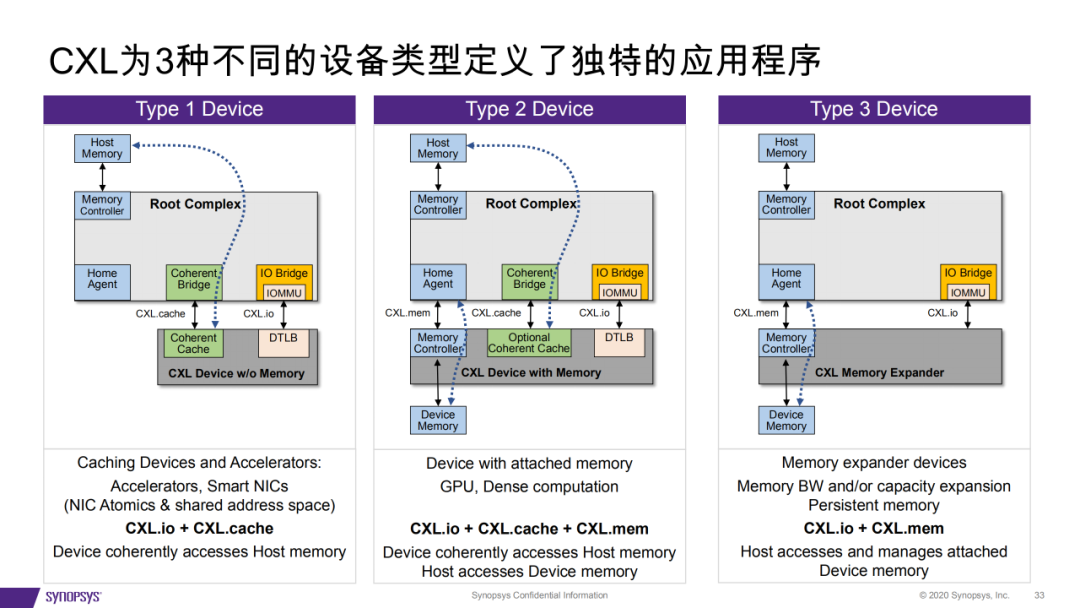

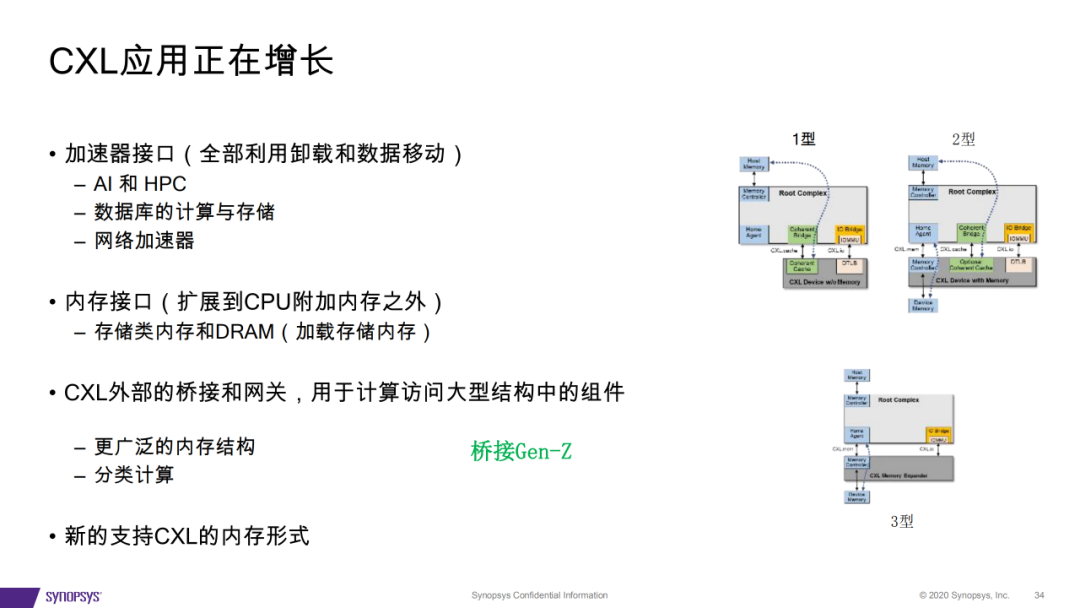

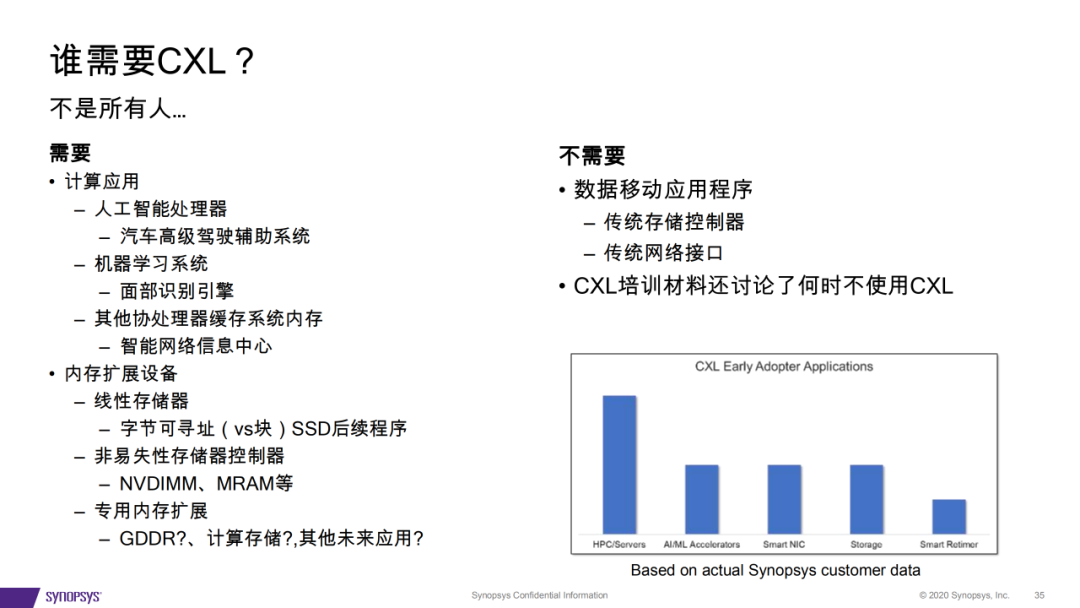

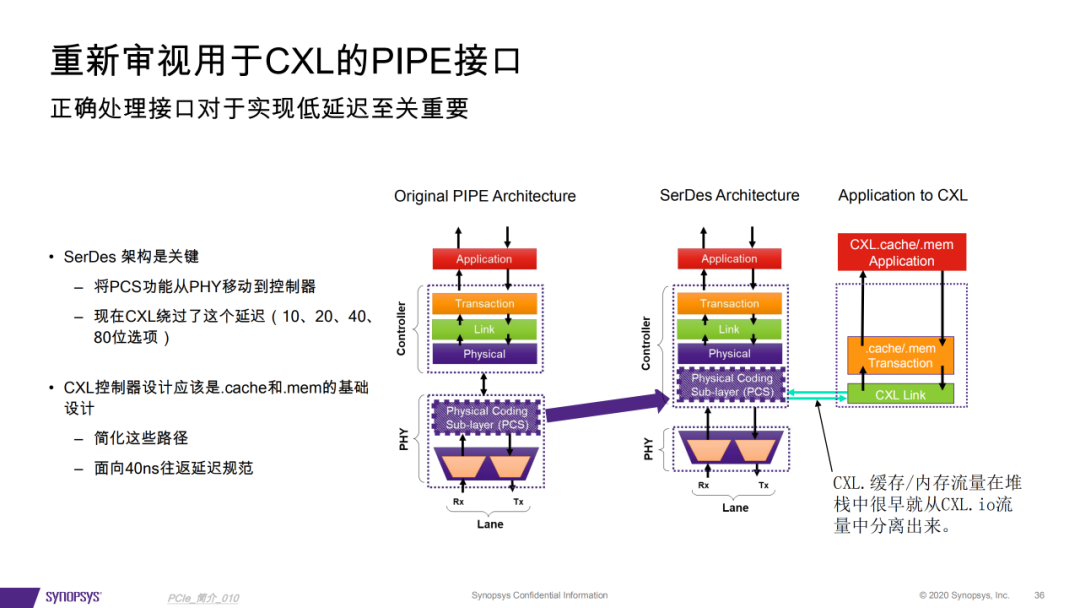

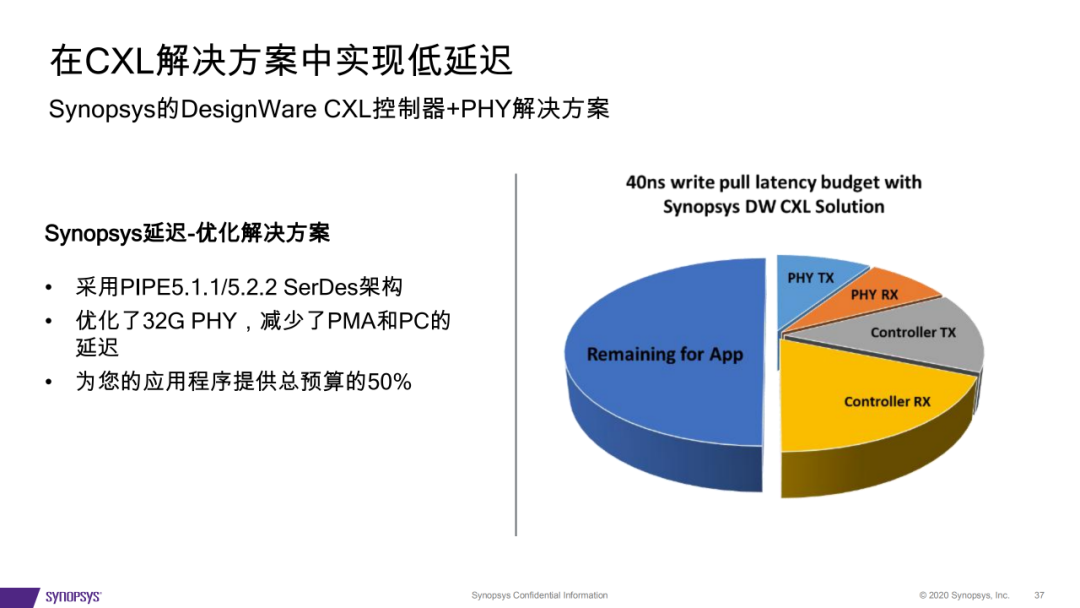

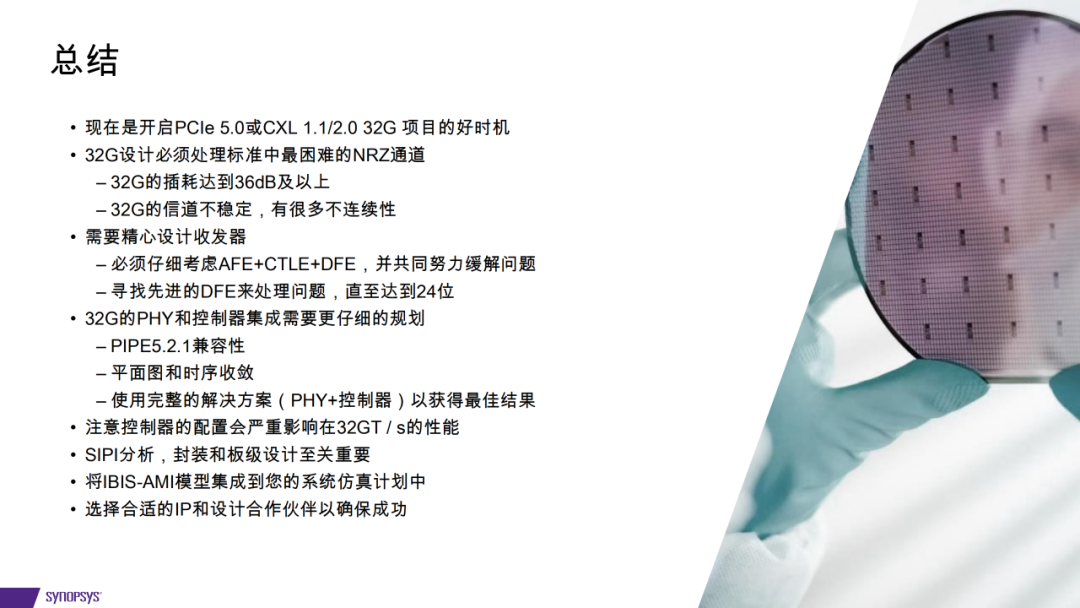

PCIe5.0和CXL最大吞吐量和最低延时设计围绕数据中心推动新的设计起点和创新,随着大数据集应用推动PCIe 5.0的采用,与此同时, AI/ML和其他数据应用的大小驱动了新的接口需求,Synopsys高性能计算的完整解决方案通过PCIe 5.0与CXL 2.0 技术提供32 GT/s吞吐率,Synopsys解决方案成功完成1GHz时序收敛,CXL内存共享,在CXL解决方案中实现低延迟。

全文下载:实现PCIe5.0和CXL最大吞吐量和最低延时设计

全文下载:实现PCIe5.0和CXL最大吞吐量和最低延时设计

下载链接:超级计算中心基础设施发展趋势

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。

评论