「指甲盖」上集成500亿晶体管!全球首款2nm芯片制程发布,未来手机四天一充电?

新智元报道

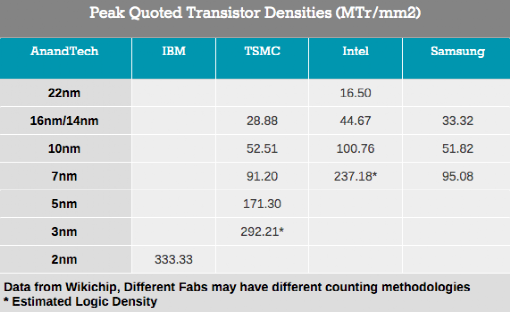

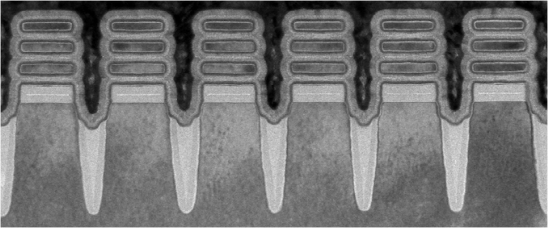

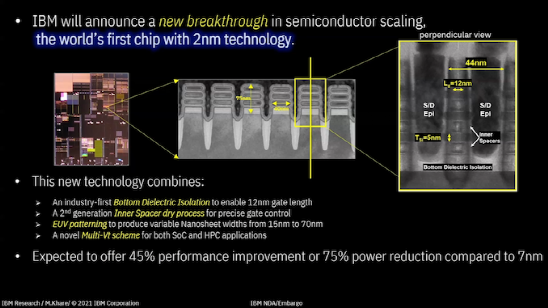

【新智元导读】将500亿个晶体管集成到指甲大小的芯片上?蓝色巨人称:我们做到了!近日,IBM宣布了他们的2纳米工艺技术,并称比目前主流的7纳米芯片快 45%,功耗减少 75%。然而,2纳米的说法却引发了当下对工艺节点名称的新思考。

手机电池寿命翻两番,只要求用户每四天给他们的设备充电一次。

减少数据中心的碳足迹,这些中心占全球能源使用量的1%,即5.8亿兆焦耳。将他们所有的服务器改为基于2纳米的处理器,有可能大大减少这一数字。

大大加快笔记本电脑的功能,从快速处理应用程序,到更容易地协助语言翻译,到更快的互联网访问。

有助于加快自动驾驶汽车等自主车辆的物体检测和反应时间。

评论