台积电走向2nm!3D封装芯片2024年将大规模量产

共

1766字,需浏览

4分钟

·

2020-11-20 15:22

编辑:QJP

【新智元导读】据中国台湾媒体报道称,台积电(TSMC) 在实现2nm工艺方面取得了重大突破,该工艺可以生产数十亿个晶体管,可能会突破摩尔定律放慢的局限。

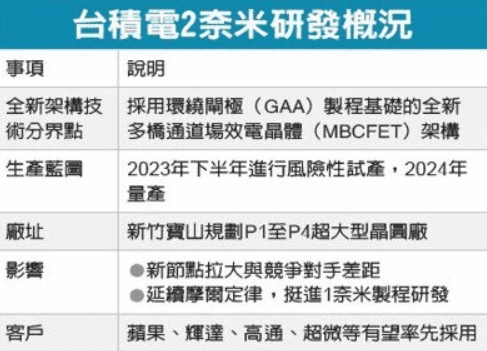

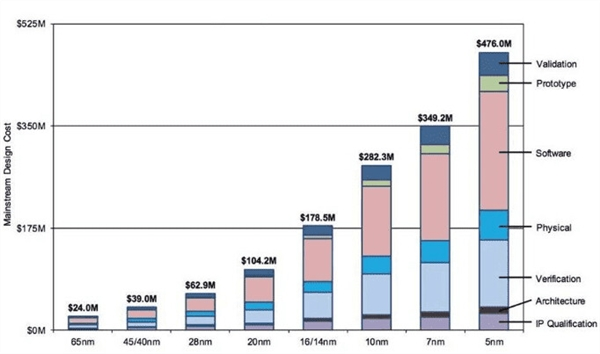

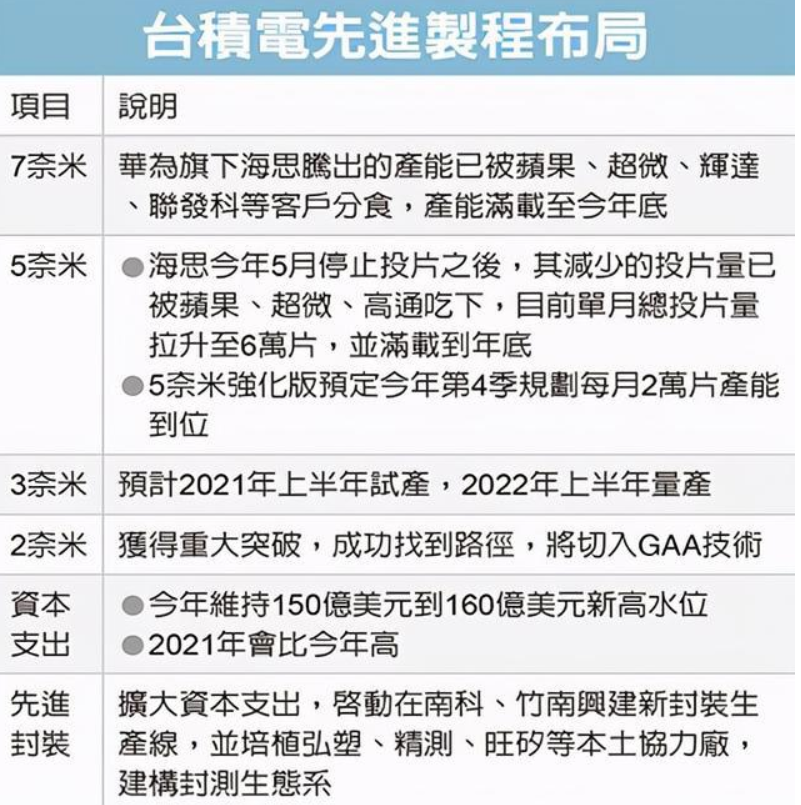

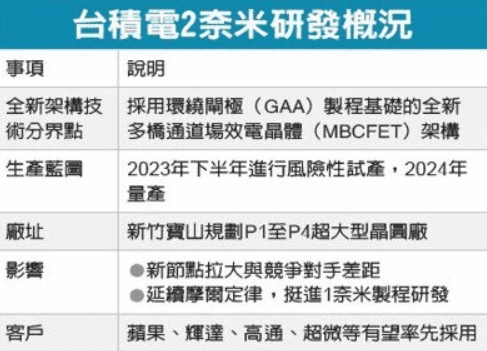

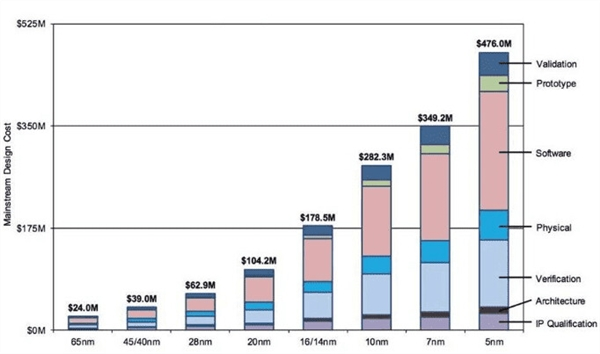

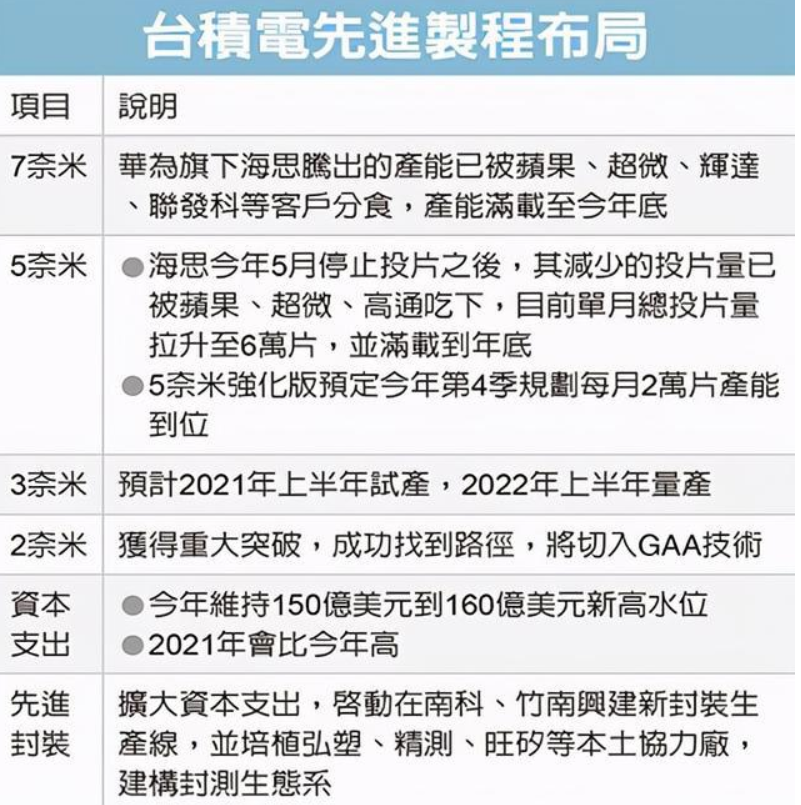

台积电于去年成立了一个研发团队,以确定其2nm技术的发展道路。据供应链来源声称, TSMC 已经确定了一个新的多桥通道场效应晶体管(MBCFET) 架构,解决了与使用 FinFET 控制工艺收缩漏电流相关的物理极限。台积电此前曾表示,其2纳米技术的研发和生产将在保山和新竹进行,同时还进一步指出,它正计划拥有四个超大型晶圆厂,占地222英亩。据台积电预计,2023年会进行小批量风险实验,未来苹果、高通、英伟达、AMD等都会成为其2nm技术的客户。根据摩尔定律,自20世纪70年代初以来,集成电路上的晶体管数量大约每18个月翻一番。最终(从现在开始可能不会持续太久) ,摩尔定律将会终结,因为硬件将不可能进一步缩小。抛弃FinFET,跨越GAAFET,直接采用MBCFET目前的芯片从2011年的22nm工艺开始就使用 FinFET,即鳍式场效应晶体管,解决了晶体管变得更小所带来的问题。直到工艺下降到 5nm前,FinFETs一直是很好的。当达到原子水平 (3纳米是25个硅原子排成一行) 时 ,FinFET 开始出现漏电现象,可能不再适用于更进一步的工艺水平。在2nm工艺上,台积电将放弃多年的FinFET(鳍式场效应晶体管),甚至不使用三星规划在3nm工艺上使用的 GAAFET (环绕栅极场效应晶体管),也就是纳米线(nanowire),而是将其拓展成为 MBCFET(多桥通道场效应晶体管),也就是纳米片(nanosheet)。GAAFET 是一个周围都是门的场效应管。根据不同的设计,全面栅极场效应管可以有两个或四个有效栅极。通过在栅极上施加电压,你可以控制源极和漏极之间的电流,将其从0切换到1,并创建一个处理器的二进制逻辑。从GAAFET到MBCFET,从纳米线到纳米片,可以视为从二维到三维的跃进,能够大大改进电路控制,降低漏电率。2nm 采用以环绕闸极(GAA)制程为基础的MBCFET架构,可以解决FinFET因制程微缩产生电流控制漏电的物理极限问题。三星也在研发 GAAFET,打算在其 3nm 芯片中引入 GAAFET,以提高超过 7nm 工艺 35% 的性能,同时降低 50% 的能耗,并在这一研发过程中投资了5亿美元。公开数据表明,2019年全球半导体公司研发支出有20家超过10亿美元,合计达到563亿美元,较2018年成长6%。其中2019年研发支出前十大半导体公司合计428亿美元,较2018年成长8%。2019年,中国有3家半导体公司研发费用过超过10亿美元,分别是台积电(TSMC)、华为海思(Hisilicon)和 联发科(MediaTek),而且全部进入前十。三家公司研发投入合计约75亿美元,较2018年增长21%。美国有8家半导体公司研发费用过超过10亿美元,合计330亿美元,较2018年增长5%;有五家进入排名前十名,分别是:英特尔(Intel)、高通(Qualcomm)、博通(Broadcom)、英伟达(nVidia)、美光(Micron)。韩国有2家半导体公司研发费用过超过10亿美元,分别是三星电子半导体事业部(Samsung Semiconductor)和 SK海力士(SK Hynix),而且全部进入前十。台积公司持续投资研究与开发,19年全年研发总预算约占总营收的 8.5%,此一研发投资规模相当于或超越了许多其他高科技领导公司的规模。台积电并没有公布为2nm新技术研发投入的经费数额,但是大家可以尽情发挥自己的想象了。

点赞

评论

收藏

分享

手机扫一扫分享

举报

点赞

评论

收藏

分享

手机扫一扫分享

举报

下载APP

下载APP