台积电太强了!兴建 2nm 生产重镇、3nm 明年试产,推 3D Farbic 封装平台

技术编辑:芒果果丨发自 思否编辑部

SegmentFault 思否报道丨公众号:SegmentFault

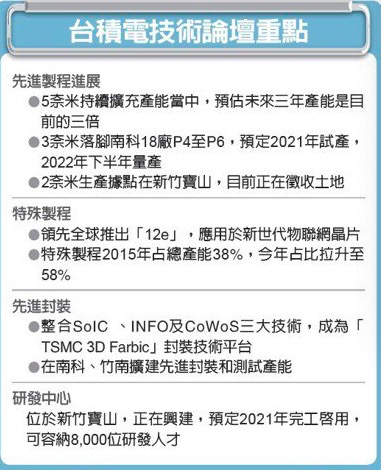

台积电昨日举行了线上年度技术论坛,其总裁魏哲家分享了台积电的最新技术进展,首度公开宣布,2nm 制程生产重镇已于新竹宝山动工兴建,预计将于明年修建完成。

有关 2nm 制程采用的规格及路径,台积电方面并未做出详细说明,但强调了将有别于 3nm 制程。台积电制程迭代的周期基本保持在两年,若按此惯例推断,2nm 制程或将于 2024 年推出。

魏哲家还宣布,台积电已将 SoIC、InFO、CoWoS 等 3D 封装技术平台整合,推出了 TSMC 3D Farbic 平台。

3 nm、4nm 明年试产,2nm 生产重镇兴建

魏哲家在讲话中提到,台积电 7nm 晶圆出货量已达到了 10 亿,5nm 已经进入量产,4nm 和 3nm 将于明年开始试产,2022 年下半年实现量产。

台积电3奈米沿用鳍式场效电晶体(FinFET)架构,据台积电公布的数据,3nm 制程与 5nm 相比,速度提升了 15%,功耗减少了 30%,晶体密度是 5nm 的 1.7 倍。

魏哲家指出,台积电将继续推进先进制程,4nm 在速度、功耗、密度上更加进步,与 5nm 有 100% 的 IP 相容性,可以沿用既有的设计基础、架构和产品创新。

台积电的 2nm 生产重镇落地新竹宝山,占地 90 多公顷,规划了 P1 到 P4 四个超大型晶圆厂,整个生产研发中心预计将于明年完工投入使用,届时将有 8000 名研发精英进驻。据了解,台积电去年的研发资金接近 30 亿美元,今年将持续扩大投资。

全球首创先进封装平台

此外,魏哲家海宣布,台积电已将前后段 3D IC 封装整合成了 TSMC 3D Farbic 平台,是全球首家具备前段 3D IC 封装能力的晶圆代工厂。

业界分析,三星稍早推出的 3D 封装技术 X-Cube 采用的是矽钻孔(TSV)进行晶圆与晶圆堆叠(WoW)的技术,适用于 7nm 和 5nm 制程生产的晶圆,台积电的 TSMC 3D Farbic 整合了前段的系统整合单晶片封装(SoIC)中的晶圆级封装 CoS 及晶圆堆叠封装(WoW),和后段的整合扇出型封装(INFO)及 CoWoS 等复杂3D封装技术,使封装服务更具整合能力。

台积电研发副总余振华将 TSMC 3D Farbic 平台视为延伸摩尔定律的重要技术突破。他强调,这个技术可以提升系统功能性、缩小晶圆尺寸,并且加快产品上市进程。

从台积电目前满载的订单来看,在 5nm 制程上再次胜过了劲敌三星,独揽了苹果新世代A14处理器代工大单。

虽然台积电对此刻意保持低调,也并未透露 2nm 制程更多细节,但根据此前的报道,台积电已找到成功路径,将切入GAA(环绕闸极)技术,迈向另一项全新的技术节点。