硅芯片拆解:早期 555 定时器芯片内部一览

微信公众号:芯片之家(ID:chiphome-dy)

555定时器

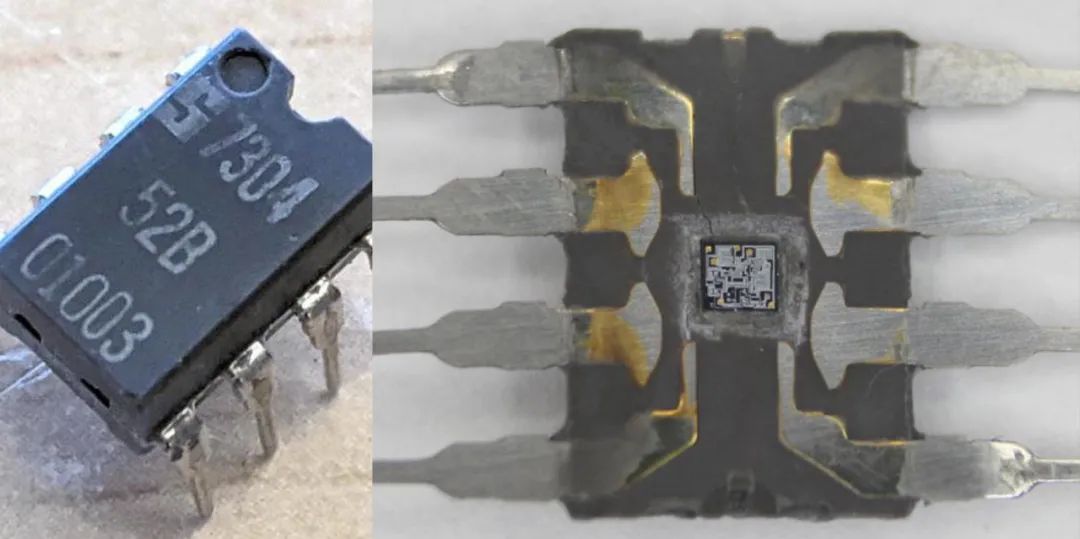

一个带有 Signetics 标志的 8 针 555 定时器。它没有 555 标签,而是标有“52B 01003”和 7304 日期代码,表示 1973 年的第 4 周。

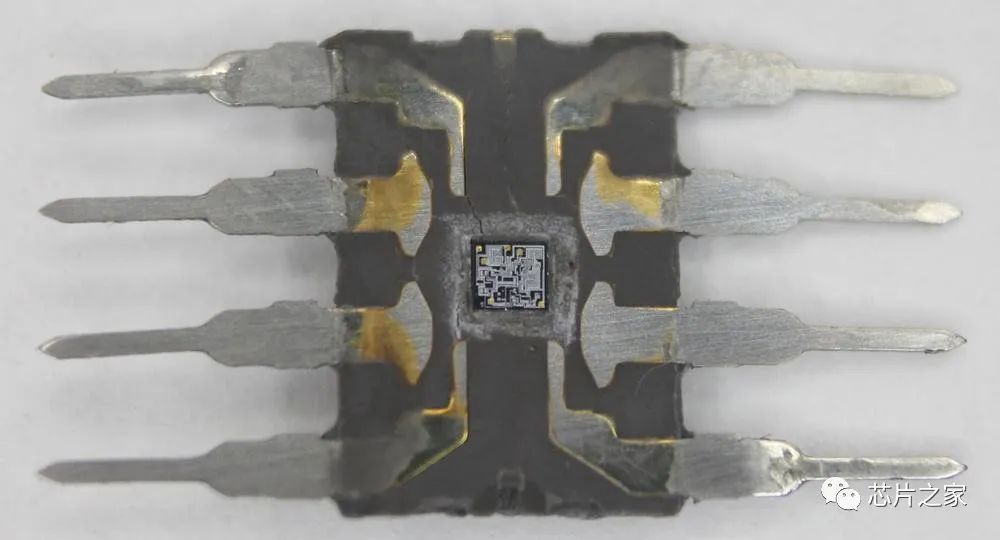

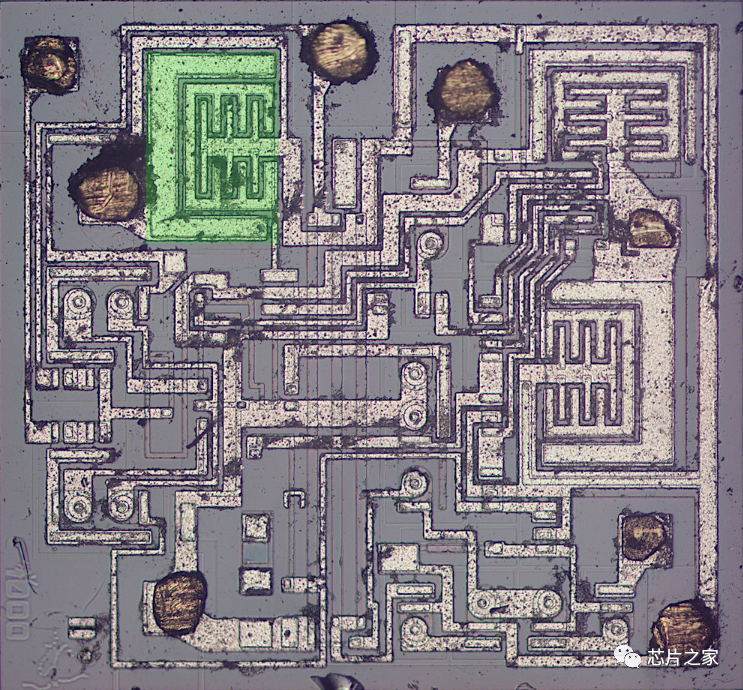

乏味地打磨环氧树脂封装以露出芯片(下图),并确定芯片是 555 定时器。Signetics 在 1972 年年中发布了 555 定时器,下面的芯片有一个 1973 年 1 月的日期代码(7304),所以它一定是最早的 555 定时器之一。奇怪的是,它没有标为 555,所以它可能是原型或内部版本。我拍摄了详细的模具照片,在这篇博文中进行了讨论。

555 定时器的封装被打磨,露出硅芯片,中间的小方块。

简要说明

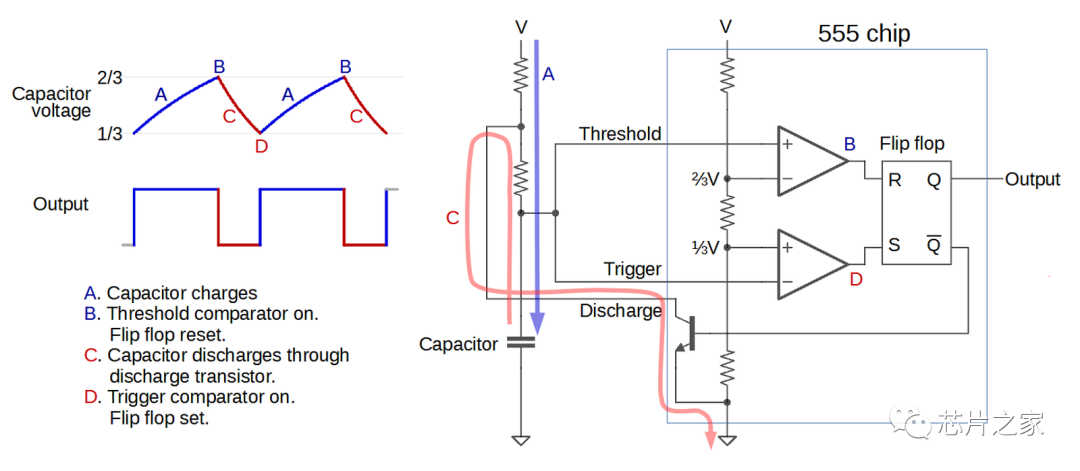

显示 555 定时器如何作为振荡器工作的图表。在 555 定时器的控制下,外部电容器通过外部电阻器进行充电和放电。

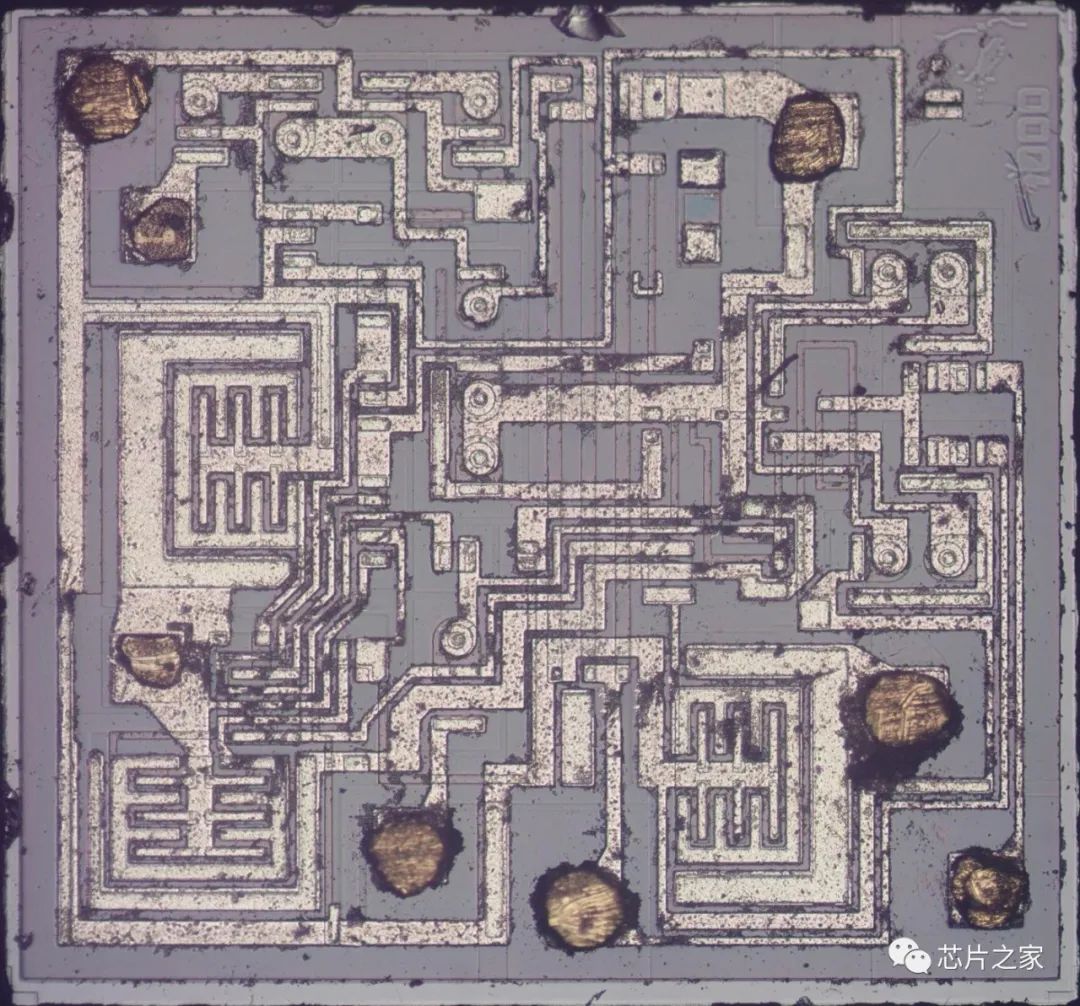

555 计时器的模具照片

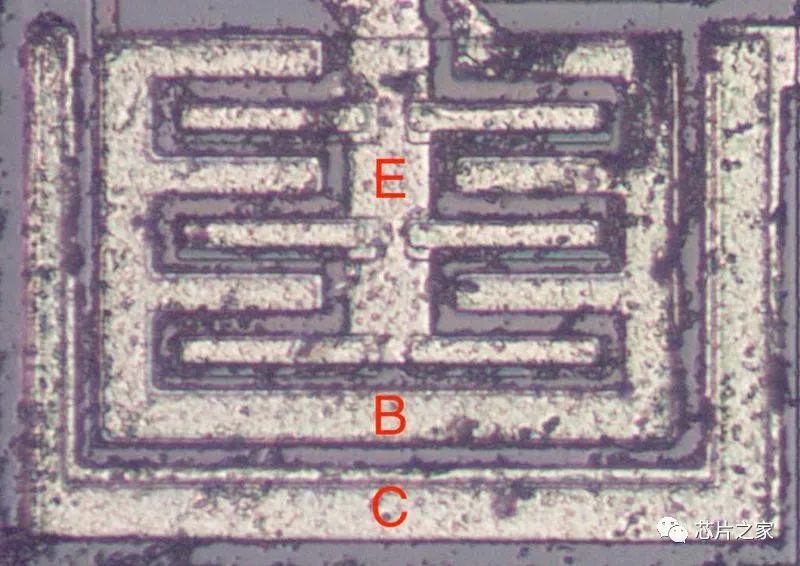

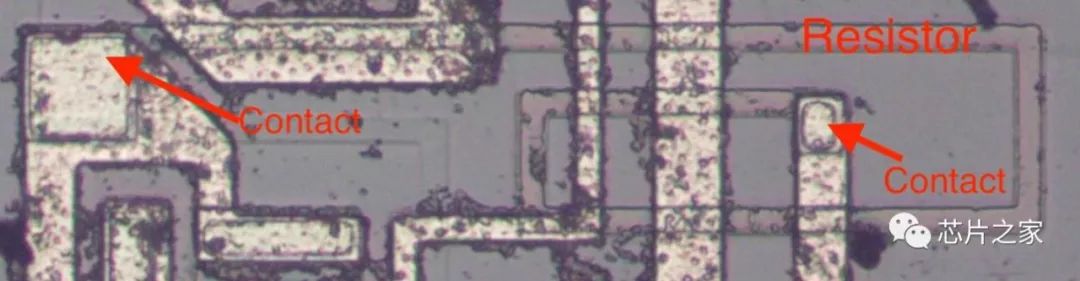

芯片上不同类型的硅更难看到。芯片的区域用杂质处理(掺杂)以改变硅的电特性。N 型硅具有过量的电子(负),而 P 型硅缺乏电子(正)。在照片中,这些区域显示为略有不同的颜色,周围有细黑色边框。这些区域是芯片的组成部分,形成晶体管和电阻器。在windows中,大家修改完hosts之后,直接保存不了,保存的时候先另存在桌面,再拖进去覆盖即可!

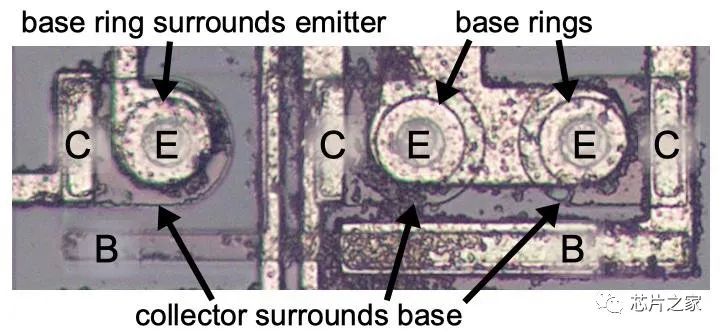

IC内部的NPN晶体管

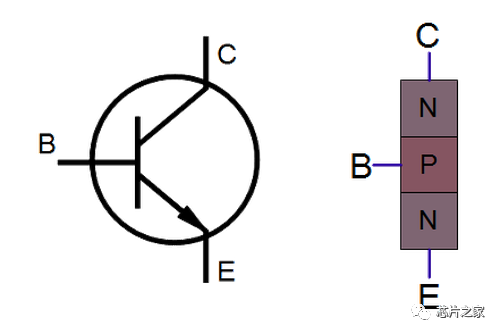

晶体管是芯片中的关键元件。555 定时器使用 NPN 和 PNP 双极晶体管。如果您研究过电子学,您可能已经看过如下图所示的 NPN 晶体管图,显示了晶体管的集电极 (C)、基极 (B) 和发射极 (E),晶体管被图示为P硅夹在两个对称的N硅层之间,NPN 层构成 NPN 晶体管。事实证明,芯片上的晶体管看起来不像这样,而且基极通常甚至不在中间!

NPN 晶体管的原理图符号,以及其内部结构的简化图

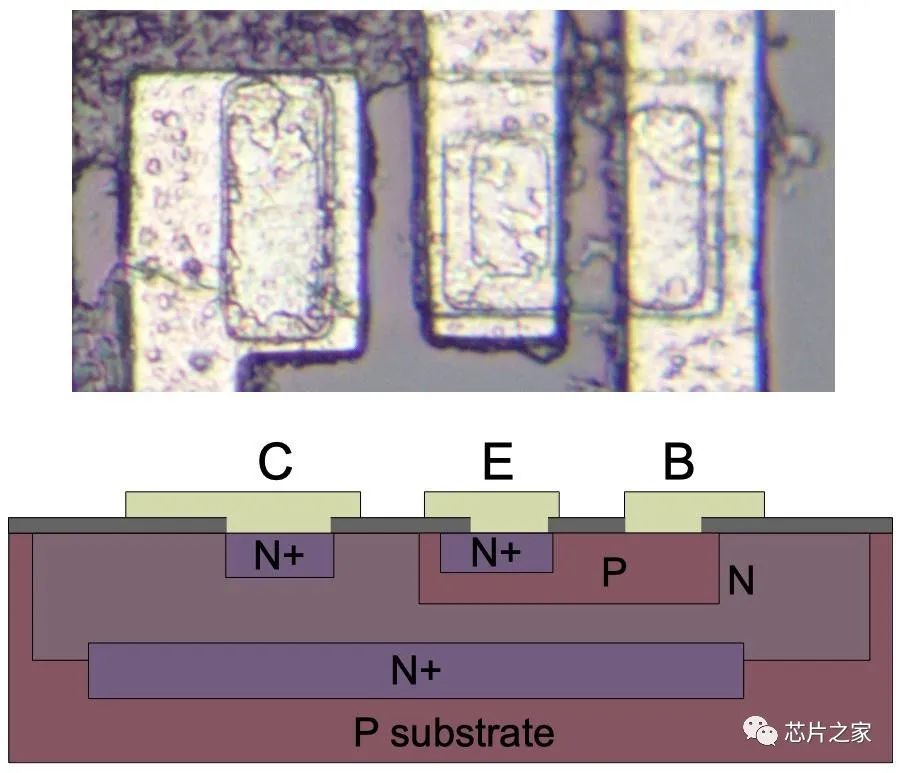

下面的照片显示了 555 中的一个晶体管的特写,因为它出现在芯片上。硅中稍有不同的色调表明已掺杂形成 N 和 P 区域的区域。白色区域是硅顶部芯片的金属层 - 这些形成连接到集电极、发射极和基极的导线。

裸片上 NPN 晶体管的结构。

照片下方是一个横截面图,说明了晶体管的构造方式。除了你在书中看到的 NPN 之外,还有很多其他东西,但如果你仔细观察“E”下方的垂直横截面,你会发现形成晶体管的 NPN。发射极 (E) 线连接到 N+ 硅。其下方是连接到基极触点 (B) 的 P 层。在其下方是(间接)连接到收集器(C)的 N+ 层。6 晶体管被 P+ 环包围,将其与相邻组件隔离。

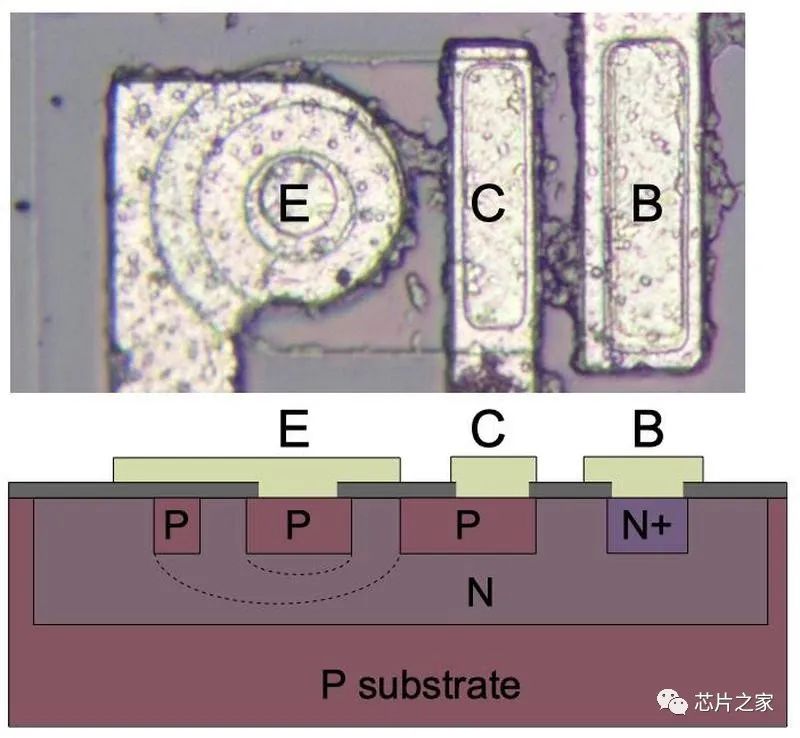

IC内部的PNP晶体管

555定时器内部的电阻。电阻器是两个金属触点之间的一条 P 硅。

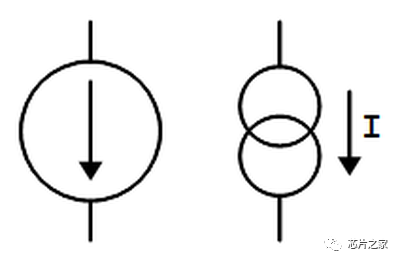

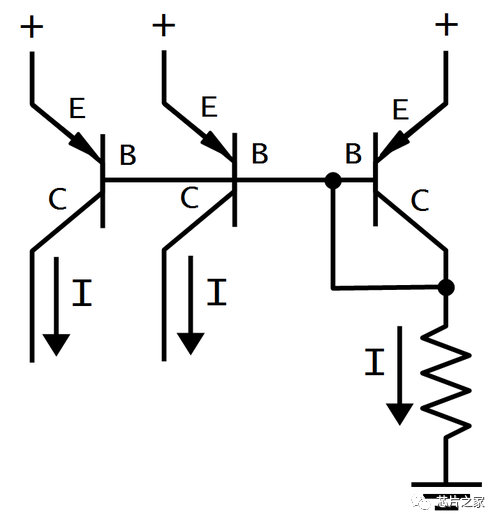

电流镜电路。右边的电流复制左边的电流。

电流镜的一个常见用途是替换电阻器。如前所述,IC 内部的电阻器既大又不准确,不便之处。尽可能使用电流镜而不是电阻器来节省空间。此外,与两个电阻器产生的电流不同,电流镜产生的电流几乎相同。

电流镜。它们都共享相同的基极,两个晶体管共享发射极。

IC元件:差分对

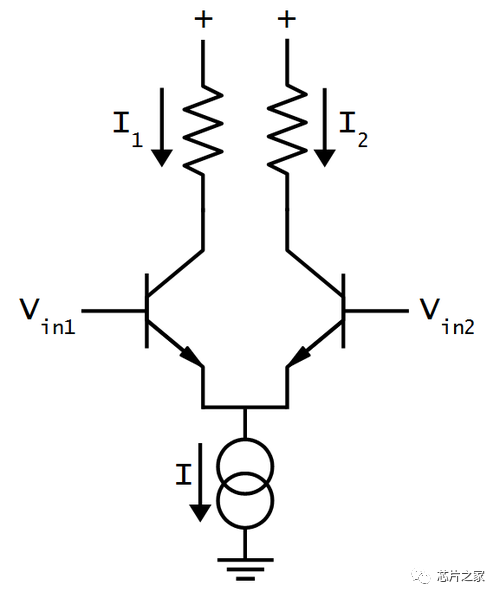

电流源通过差分对发送固定电流 I

上面的示意图显示了一个简单的差分对。底部的电流源提供固定电流 I,该电流在两个输入晶体管之间分配。如果输入电压相等,则电流将平均分成两个分支(I1 和 I2)。如果其中一个输入电压比另一个高一点,则相应的晶体管会以指数方式传导更多的电流,因此一个分支获得更多电流,而另一个分支获得更少。一个小的输入差异足以将大部分电流引导到“获胜”分支,从而打开或关闭比较器。555 芯片使用一个差分对作为阈值比较器,另一对作为触发比较器。

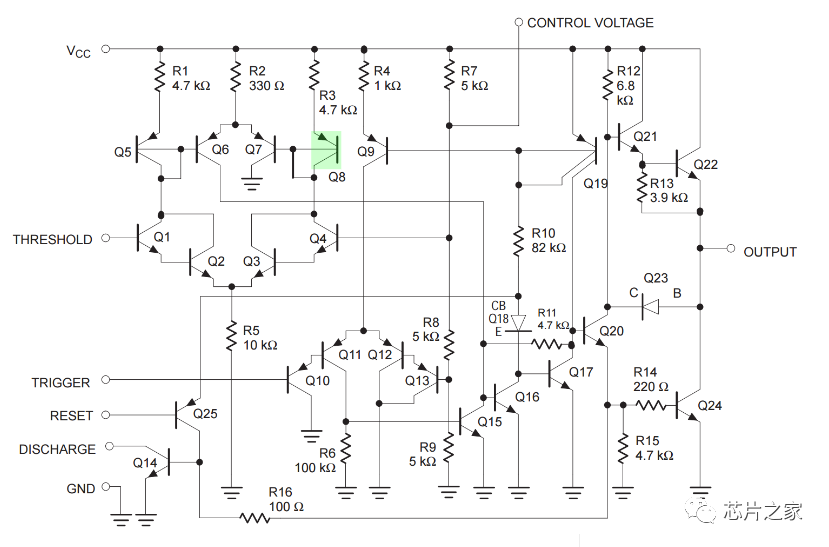

555原理图

http://www.righto.com/2022/01/silicon-die-teardown-look-inside-early.html

https://shop.evilmadscientist.com/productsmenu/tinykitlist/652

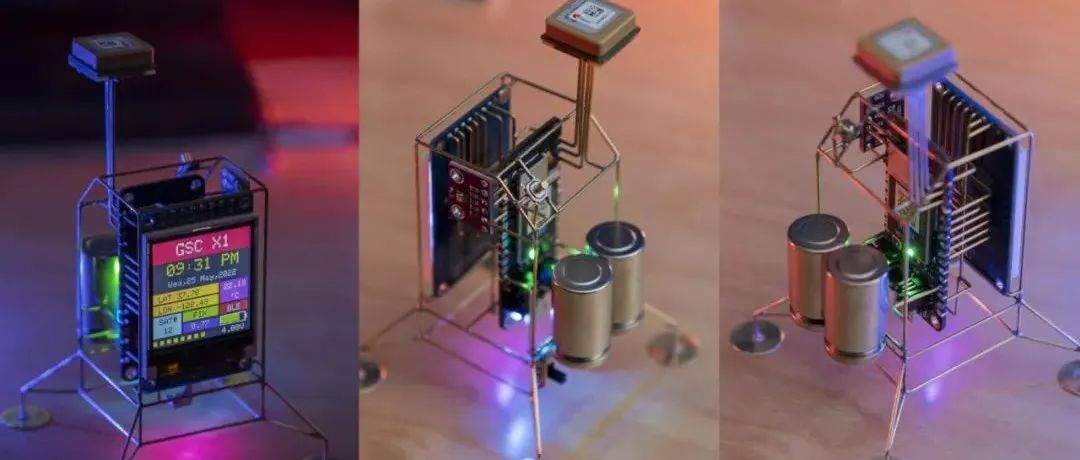

超具艺术感的电子搭棚艺术品

深度长文:STM32是如何软硬件结合,编译后怎么样一步步运行起来的

一位嵌入式前辈 8 年的工作总结,强!

电子漫画系列套图更新11张,共计83张,附高清无码下载链接

欢迎点分享、收藏、点赞、在看。