AMD Zen 4架构路标:2022年Genoa 96核,2023年Bergamo 128核

导读:今年7月,英特尔公布了新的路线图,4年内要完成5代产品迭代,推出IDM2.0战略快速进入Intel 20A制程工艺,参见“英特尔技术创新战略线路图”。AMD和Intel在芯片领域的尖峰对决一直没有停歇。

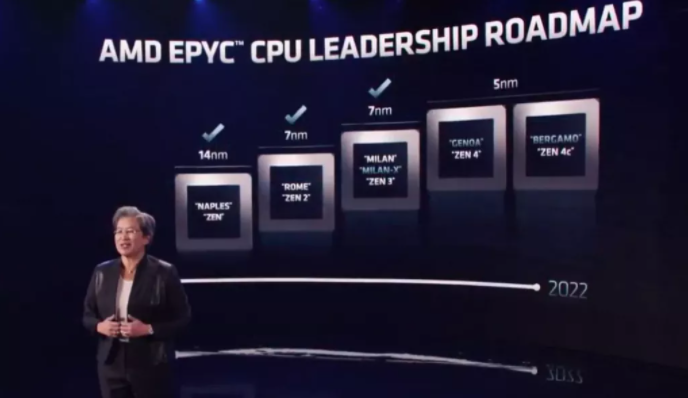

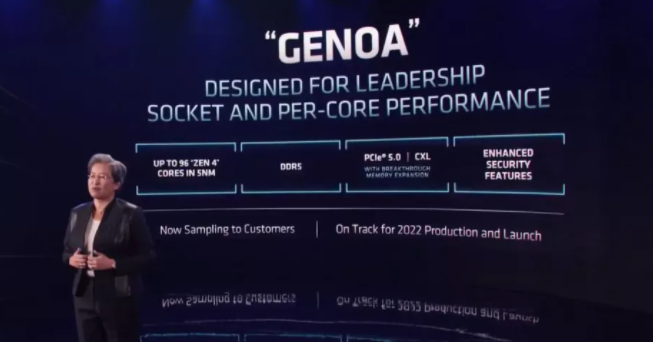

AMD 首席执行官 Lisa Su 今天在其 AMD 加速数据中心活动中分享了该公司的 Zen 4 CPU 路线图,包括 96 核 Genoa 型号和 128 核 Bergamo 芯片。在 AMD 推出具有高达 768MB 三级缓存和 Instinct MI250X GPU的EPYC Milan-X 芯片之后,这为活动增添了不少亮点。

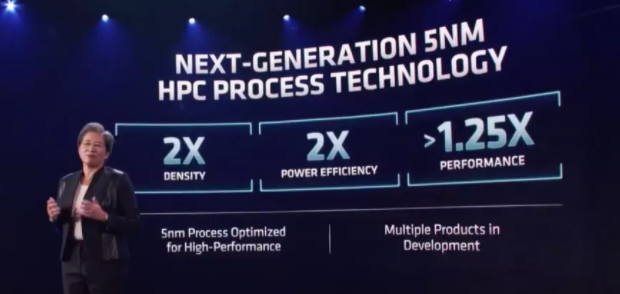

AMD 还分享了其将用于新 Genoa 和 Bergamo 芯片的 5nm TSMC 工艺的第一个细节,声称与 AMD 用于其当前一代芯片的 7nm 工艺相比,它提供两倍的密度和功率效率以及 1.25 倍的性能。

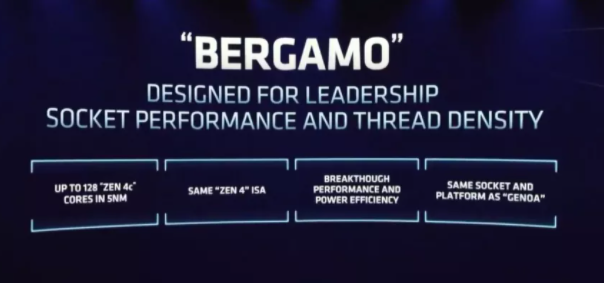

新路线图涵盖第四代 EYPC 处理器。其中96 核 Genoa 将在 2022 年亮相,采用 5nm 工艺,而同样采用 5nm 工艺的 128 核 Bergamo 将于 2023 年上市。此外,Bergamo 还配备了一种新型的“Zen 4c”内核,针对特定用例,这意味着 AMD 的 Zen 4 芯片将配备两种类型的内核,大概闹钟功能的“c”内核显然是较小的变体。

这是 AMD 针对 Zen 4 CPU 路线图的 TLDR:

“Genoa”将拥有多达96个高性能“Zen 4”内核,在DDR5和PCIe Gen 5中实现下一代内存和I/O技术,并驱动平台能力完美平衡Zen 4内核、内存和I /O 提供领先的效率;

“Bergamo”是一种高核数计算引擎,专为需要高密度线程密度的云原生应用程序而定制。拥有 128 个高性能“Zen 4 C”内核;

“Bergamo”具有与 Genoa相同的所有功能,包括DDR5、PCIe 5、CXL 1.1、相同的RAS和全套Infinity Guard安全功能,并且与热那亚插座兼容

Genoa将采用台积电的 5nm 工艺,AMD 表示,5nm 的密度和功率效率是为当前一代 EPYC Milan 芯片提供动力的 7nm 工艺的两倍。它还提供 7nm 工艺 1.25 倍的性能。这对于以消费者为中心的 Ryzen Zen 4 芯片来说也是个好兆头。

EPYC Genoa 芯片将拥有多达 96 个 Zen 4 内核并支持 DDR5 和 PCIe 5.0,以及允许设备之间一致内存连接的CXL 1.1 接口。该芯片将解决 HPC 和通用数据中心、企业和云工作负载,Su 表示它将扩展每核和socket级(多线程)性能。Genoa现在正在向客户提供样品,并有望在 2022 年推出。

Bergamo 也采用 5nm 工艺制造,单个芯片中将配备多达 128 个内核。

AMD 创造了一种新的“Zen 4c”类型的 Zen 4 核心,“c”表示该核心专为云原生工作负载而设计。Zen 4c 内核在 5nm EPYC Bergamo 中首次亮相,它与 Genoa 插槽兼容,并使用相同的 Zen 4 指令集。这意味着您可以将这些芯片放入与 Genoa 型号相同的服务器中。

这些“c”核心可能比将在Genoa 首次亮相的标准 Zen 4 核心小,在其中删除了某些不需要的功能以提高计算密度。但是,这些芯片具有密度优化的缓存层次结构以增加内核数量,从而解决需要更高线程密度的云工作负载。这可能意味着芯片具有较小的缓存,或者缓存级别可能已被删除,但 AMD 尚未分享详细信息。

AMD 确实表示,Bergamo 将提供更高水平的电源效率和每个插槽的性能。Bergamo 将于 2023 年上半年发货。它具有与热那亚相同的整体功能集,因此具有 PCIe 5.0、DDR5 和 CXL 1.1。

随着 AMD 越来越接近推出这些处理器,我们一定会了解更多。敬请关注。

AMD Zen 4架构细节曝光

日前,业内人士Hans de Vries曝光了Zen 4的部分CPU设计架构细节,据说来自前不久某硬件大厂遭勒索软件攻击后泄露到黑市的机密文档。

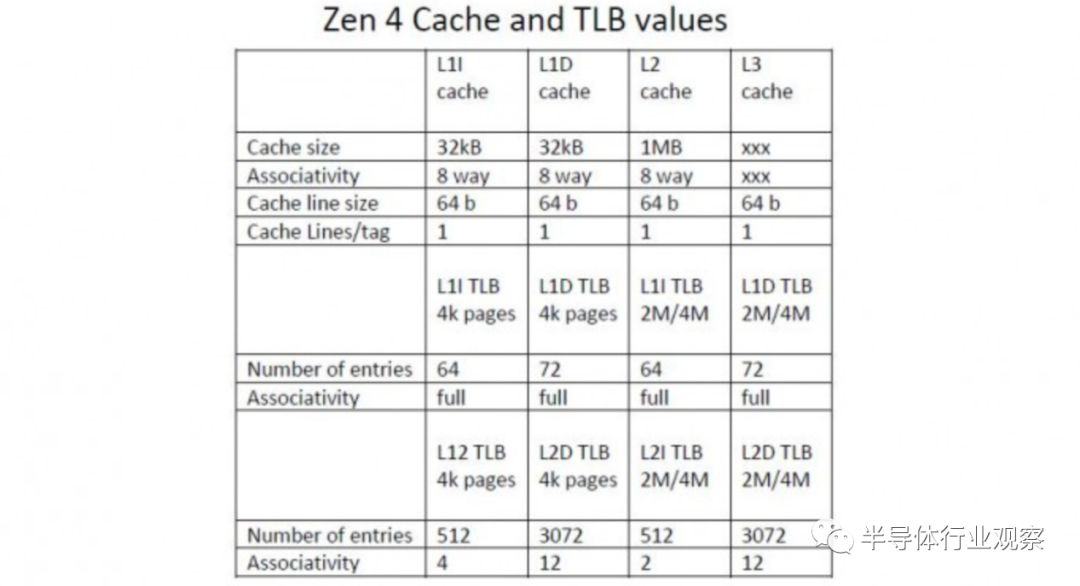

图标概述了Zen 4的缓存部分,对比Zen3,一级指令/数据缓存大小没变,依然是32KB、关联8路,但二级缓存(指令+数据)则从512KB翻番到1MB,依旧是关联8路。

遗憾的是,三级缓存的容量未公布,看来有惊喜,上一代Zen3是每个CCD(8核Die)共享32MB。

不过可以比较12代酷睿Alder Lake体系中,Golden Cove(P核,性能核)每个核心1.25MB二级缓存,Gracemont(能效核,E核)则是每四个核心2MB,也就是二级缓存最多14MB,这意味着Zen4的物理16核(16MB L2)会再次反超。

通常来说一级、二级缓存在分支预测中扮演极为重要的角色,它也是IPC指标增幅的重要支撑。按照AMD此前的说法,Zen4之于Zen3的变化幅度不会小于Zen3之于Zen2,后者的IPC当时增加了19%,5nm Zen4非常可期,况且还有后发优势一说。

2、信创产业研究框架

3、ARM行业研究框架

4、CPU研究框架

5、国产CPU研究框架

6、行业深度报告:GPU研究框架

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。