CCIX缓存一致性互联技术概述

缓存一致性的加速器互联,即 CCIX™(读成“see 6”)是一种能够将两个或两个以上器件通过缓存一致性的方式来共享数据的片间互联。机器学习和大数据应用正深刻的变革数据处理的方式。通过片外加速器的定制,传统处理器从计算到网络的应用都得到了增强;这推动了产业整体向加速器和异构计算发展。对目前很多计算任务,加速器能够比单独的处理器速度更 快、功耗更低的完成所需功能。

下载链接:

今天,高科技的版图是由新的、大规模的消费者服务的创新构成的,例如 5G、云计算、物联网、大数据和自动驾驶。机器学 习和人工智能应用根本性的改变了消费者行为。这又推进了平台和解决方案不断演进,通过高效、可扩展的方式来支持这些新应用。仅以中央处理器为中心的服务器架构的解决方案无法满足这些应用的性能需求。因此需要基于高效的异构计算架构的解决方案,包含加速器例如图形处理单元(GPU)、可编程逻 辑阵列(FGPA)、智能网卡(NIC)和很多其它领域特定的可编程器件。PCI Express™ (PCIe™) 是目前最常见的,处理器和片外加速器间传输数据的协议。尽管 PCIe 协议作为输入输出(IO)协议很有效,但不能支持 IO 设备成为对等计算模型中的一 个无缝组件。随着片外加速器的应用越来越多,高性能、低延时和易用性成 为下一代互联的首要诉求。

高性能、低延时的片间互联接口是任何基于片外加速器的系统的关键部分。产业成功的很重要的一点是,处理器、加速器和其它外设的厂商能获得一个非私有的标准来保证片间的无缝传输。这样一个标准的强烈诉求促成了 CCIX 联盟的成立,CCIX联盟由一群有共同理念、希望解决片外加速器互联需求的公司组成。通过变革加速器的内存和数据移动的方式,这个新的互联标准对使能下一代平台和解决方案起到关键作用。

CCIX 采用两种机制来提高性能、降低延时。第一种机制是采用缓存一致性,自动保持处理器和加速器的缓存一致,提升易用性、降低延时。第二种机制是提高 CCIX 链接的原始带宽。最高链接速率升至 25GT/s (千兆传输/秒)。CCIX 规范也规定了多个CCIX 端口如何聚合提供超过单个接口的性能,匹配加速器和内存扩展带宽。

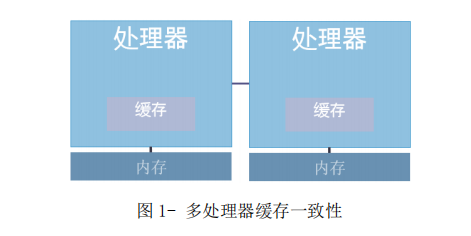

多处理器系统已经部署了确保不同处理器缓存一致性的技术。将现有缓存一致性互联的基本原理扩展到加速器,应用数据就可以在处理器缓存和加速器缓存间自主传递,不需要软件驱动参与数据传递。除了缓存,CCIX 还支持操作系统分页的内存(系统内存)扩展包含 PCIe 设备带的内存。CCIX 的数据共享模型是基于以虚拟地址(VA)寻址的共享内存。

处理器和加速器的缓存和/或内存通过 CCIX协议自动更新。因为数据通过 CCIX 协议自动同步,只需要传递数据指针而不需依赖复杂的直接内存访问(DMA)驱动。自动同步能减小数据延时,提升应用性能。同时减小了软件开发者的负担,使他们聚焦于应用而不是加速器和主处理器间数据传递的底层机制。

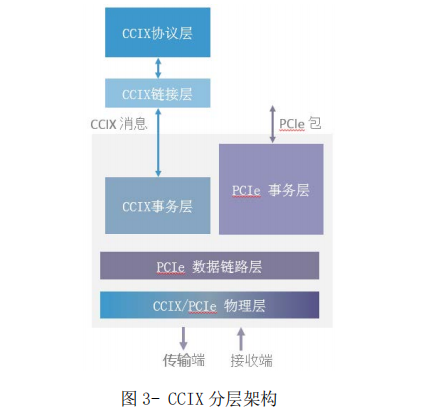

CCIX 架构是从 PCI Express 基本架构扩展的分层架构。一般来看,CCIX 可看作两个主要规范,包含各层级协议。CCIX 协议规范包含 CCIX 协议层和 CCIX 链接层。这些层规定缓存一致性协议、报文发送、流控和 CCIX 传输部分的协议。CCIX 传输规范包含 CCIX 和 PCIe 事务层,PCIe 数据链路层,和 CCIX 物理层。这些层负责器件间的物理连接,包括速率和带宽协商,传输包错误检测和重试,和初始包编码协议。

CCIX 栈的最上层是 CCIX 协议层。这一层负责一致性协议,包括内存的读、写流。这一层提供了片上一致性协议(例如 Arm AMBA CHI)的简单映射。这一层定义的缓存状态使得硬件能够确定内存的状态。比如硬件可以确定数据是否唯一且未被修改(和内存一致),或是共享且被修改的(和内存不一致)。

CCIX 协议层之下是 CCIX 链接层。这一层负责 CCIX 协议层定义的代理(agent)之间消息的传输格式。目前 CCIX 链接层是构建在 PCIe 之上,但是基于分层架构,CCIX 将来可以映射到不同的传输层。此外,这一层负责端口聚合,使得多个端口能够聚合在一起提升带宽。

CCIX 和 PCIe 事务层负责处理它们各自的包。PCIe 协议支持部署虚拟通道,使得不同数据流通过一个 PCIe 链路。将 CCIX 和 PCIe 传输流各分到一个虚拟通道,CCIX 和PCIe 传输可以共享相同的链路。CCIX 能够传输标准的 PCIe 包,或经过优化的 CCIX 包。经过优化的 CCIX 包删减了 PCIe 包里的几个不必要的字段。传输标准的 PCIe 包时可以采用现有的 PCIe 交换器。传输经过优化的 CCIX 包,能降低 PCIe 的额外开销,使得一致性传输的包更小、更高效。

PCIe 数据链路层执行数据链路层的所有正常功能。这些功能包括 CRC 错误校验、包确认和超时检查,和信用初始化及交换。

CCIX/PCIe 物理层的基础是 PCIe 物理层。CCIX 扩展了物理层来支持 25GT/S(千兆传输/秒)。这个较快的速率称为 ESM(扩展速率模式),会在两个具备 ESM 模式的器件连接时自动识别,速率比当前的第四代 PCIe 速率 16GT/S提升 56%。

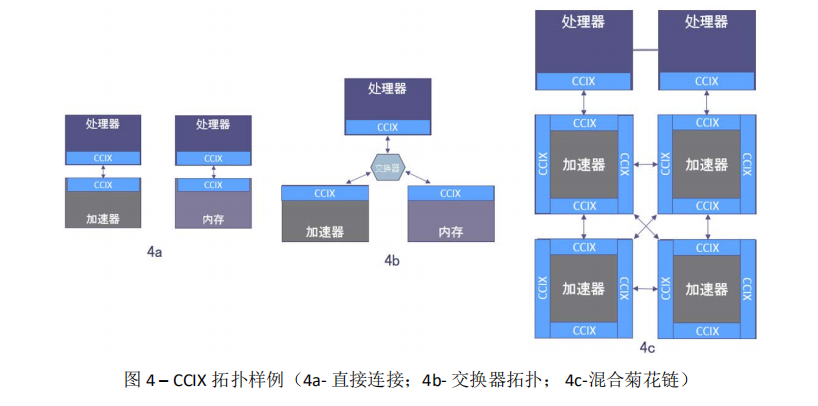

得益于分层架构,CCIX 能够支持多种灵活的拓扑结构。最常见的拓扑结构是直接附加的共享虚拟内存。但其它拓扑结构,如交换器、菊花链或网状拓扑,也很容易被构建和支持。

CCIX 协议定义了 CCIX 组成模块的内存访问协议。所有 CCIX 器 件至少有一个具备 CCIX 链接的端口。一个 CCIX 端口关联一组物理管脚,用于和另一个 CCIX 端口连接,在两个或多个不同芯片间交互信息。

同时定义了一些不同的代理类型,哪种代理在哪一个器件取决于器件的功能。定义的代理类型包括:请求代理(RA)、主代 理(HA)、从代理(SA)和错误代理(Error Agent)。请求代理、主代理、从代理、错误代理,系统里的端口和链接统称CCIX 组件。一个代理在协议中由一个代理 ID 标识。以下对每一种代理类型进行简要描述。

基于上述的代理类别,可以描述 CCIX 可见的一些常见用例。

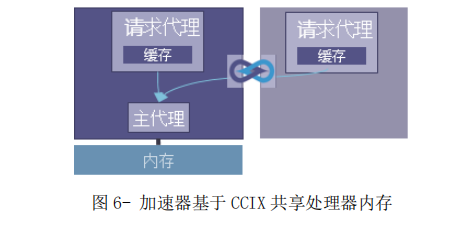

加速器共享处理器内存:当采用和部署 CCIX 时,最常见的初始用例是处理器和加速器共享缓存。这个用例里有两个请求代理,各自管理自己的缓存。主代理在处理器上,管理连接到该处理器的内存的访问。

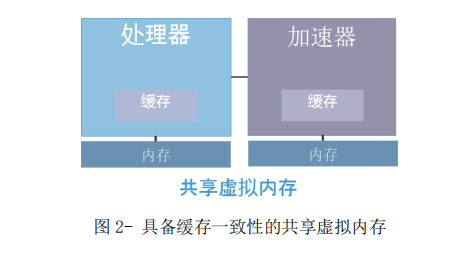

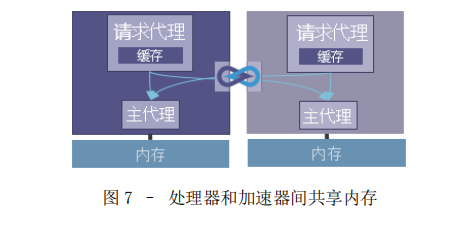

共享的处理器和加速器内存:下一种常用模型可能是处理器和加速器共享虚拟内存。在这个用例里,加速器和处理器的内存同在一个共享虚拟内存池里。处理器只需要简单的将待处理的数据的地址指针传给加速器,而不需要复杂的 PCIe DMA 和驱动在处理器和加速器内存之间传递数据。有两个请求代理管理各自的缓存,有两个主代理管理内存。免去软件驱动开发和额外开销,可以大幅提升系统性能和简化软件。

拓展基本结构:得益于 CCIX 非常灵活的特性,它可以在展示的这些基本数据流之外进行拓展。从直接附带的加速器、到网状拓扑和星型网络, CCIX 具备很可观的选项来支持很多种类的拓扑结构。

CCIX 联盟是一个开放的工业标准组织,制定独立于任何处理器架构的、非私有的 CCIX 标准。CCIX 标准为内存扩展器件和加速器提供高性能、低延时、芯片与芯片间的互联。它特别为应 对未来数据中心、云计算、大数据及其它需要异构计算的应用的巨大挑战而设计。CCIX 标准将是革命性的进步,它拓展了开放、异构架构和缓存一致性共享内存模型的优势,来满足未来数据中心不断演进的需求。

下载链接:

2、信创产业研究框架

3、ARM行业研究框架

4、CPU研究框架

5、国产CPU研究框架

6、行业深度报告:GPU研究框架

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。