史无前例!ChatGPT能设计芯片了,谷歌&英伟达&三星更早都在布局!

资料来源:arXiv等

作者:詹士 Enzo

物联网智库 原创

导读

一个“好奇”翻开了生成式AI的另一面

生成式AI应用于芯片设计并非首次

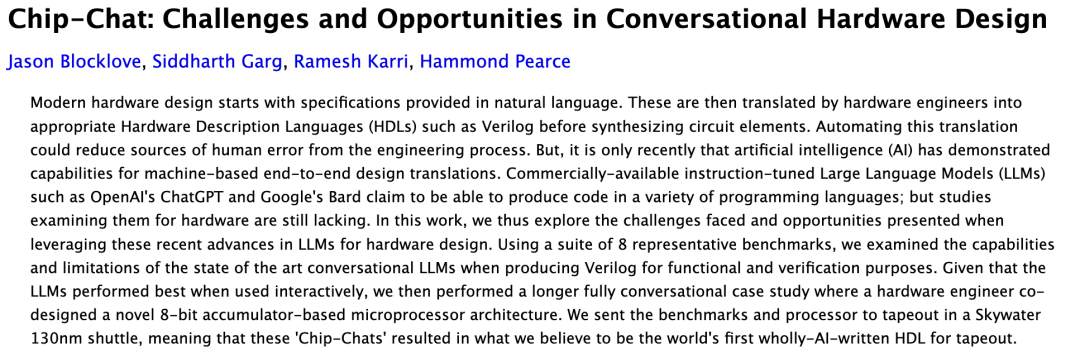

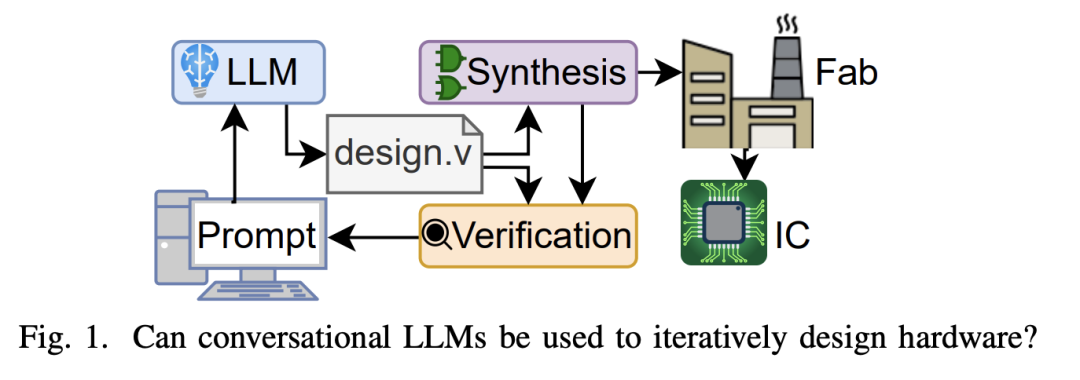

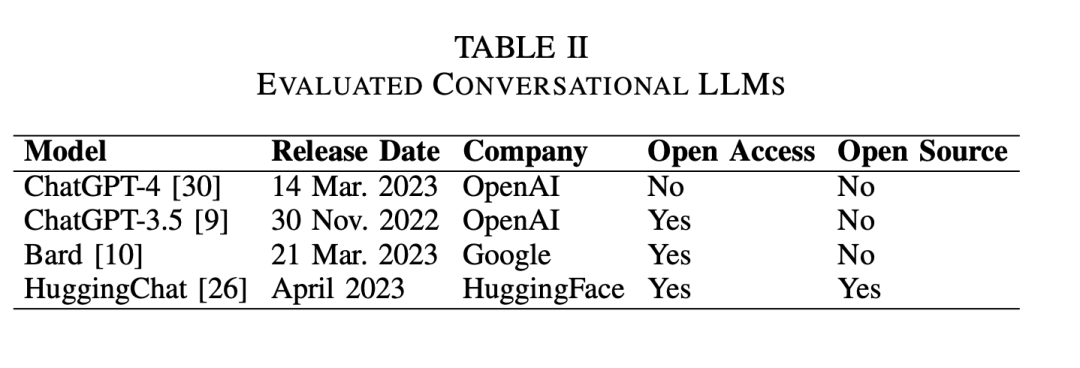

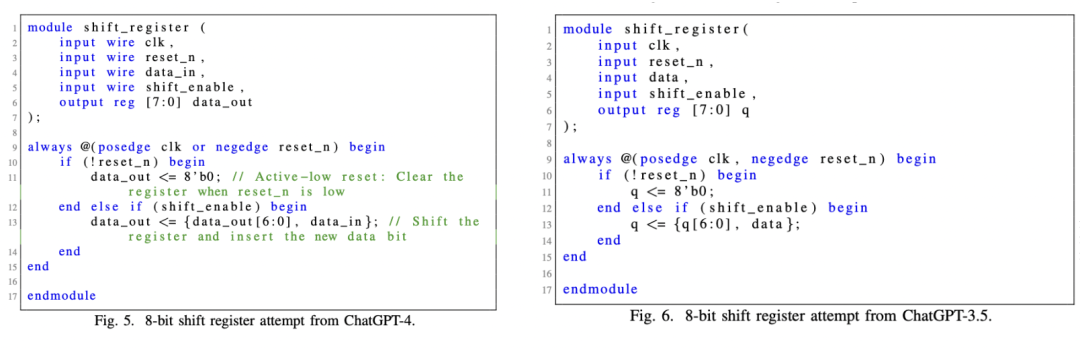

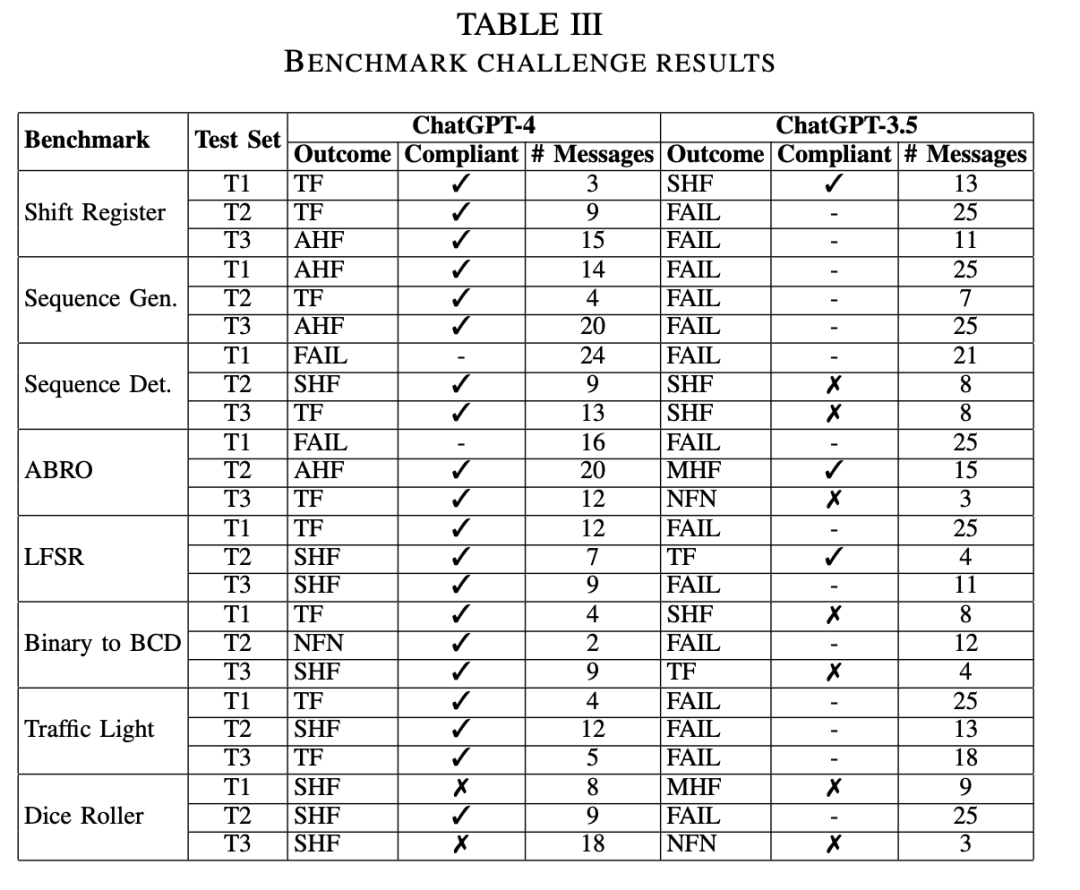

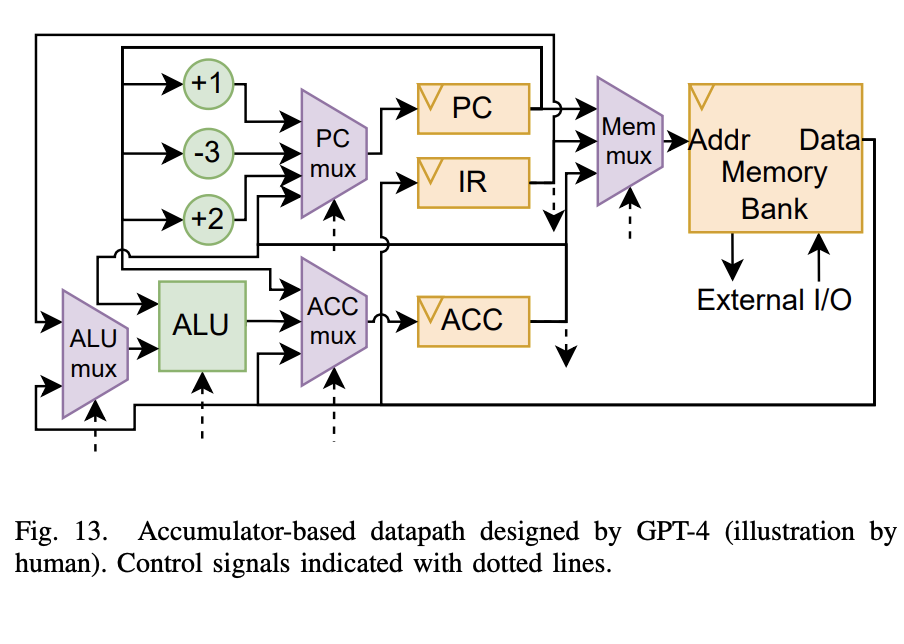

1.《Chip-Chat: Challenges and Opportunities in Conversational Hardware Design》,Jason Blocklove, Siddharth Garg, Ramesh Karri, Hammond Pearce

2.《Chip Chat: Conversations with AI models can help create microprocessing chips, NYU Tandon researchers discover》,NYU TANDON

3.《Exclusive Interview: NYU Team Taps ChatGPT to Design Processor From Scratch》,Jake Hertz

评论