DPU演化、技术派别和玩家

编者注:Fungible最先于2016年提出DPU(Date Processing Unit)的概念,也是第一家专注于设计DPU的创业公司。Nvidia于2020年在收购Mellanox(提供基于IB、以太网的计算机网络产品)后,同年提出BlueField DPU,自此,DPU开始活跃起来,国外Marvell、Pensando、Broadcom、Intel等纷纷加入,国内中科驭数、星云智联等也通过自身的技术积累入局DPU。

下载链接:

在维基百科中,DPU是一种具有硬件加速数据处理功能的可编程的用于数据中心计算的专用电路(a programmable specialized electronic circuit with hardware acceleration of data processing for data-centric computing)。定义比较宽泛,FPGA以及一些交换机芯片粗略地看,也能归于“DPU”一类,只划分了DPU的功能表现。

Fungible的DPU能实现跨数据中心规模的计算和存储资源的隔离的设备(Enabling hyper disaggregation of compute and storage resources across data center scales)。Fungible的DPU侧重于计算(CPU)与存储的隔离,显然DPU承担的任务不仅仅于此。

Marvell设计的DPU用于无线基础设施和网络设备,包括交换机、路由器、安全网关、防火墙、网络监控和智能网卡(Designed for use in wireless infrastructure and networking equipment including switches, routers, secure gateways, firewall, network monitoring, and smartNICs.)。这种定义,将DPU视为网卡的一种延申,不能够解决数据中心面临的所有问题。

Nvidia的DPU需要具备工业标准、软件可编程的多核CPU;高性能的网络接口和可编程的加速引擎(System on a chip that combines: Industry-standard, high-performance, software-programmable multi-core CPU ; High-performance network interface and Flexible and programmable acceleration engines)。

Nvidia通过具体的组成定义DPU,与CPU具有五大部分的组成(计算、存储、控制、输入、输出)定义类似,但仍难以描述清楚DPU,是什么本质特征,能让其承担CPU、GPU之后又一大算力支柱。

但从上述的定义中,可以总结出DPU涉及的领域有网络、安全和存储。从DPU承担的功能的历史变化中,去总结DPU需要解决的问题。

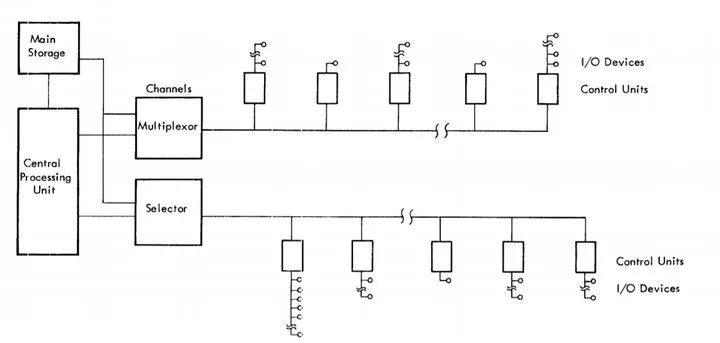

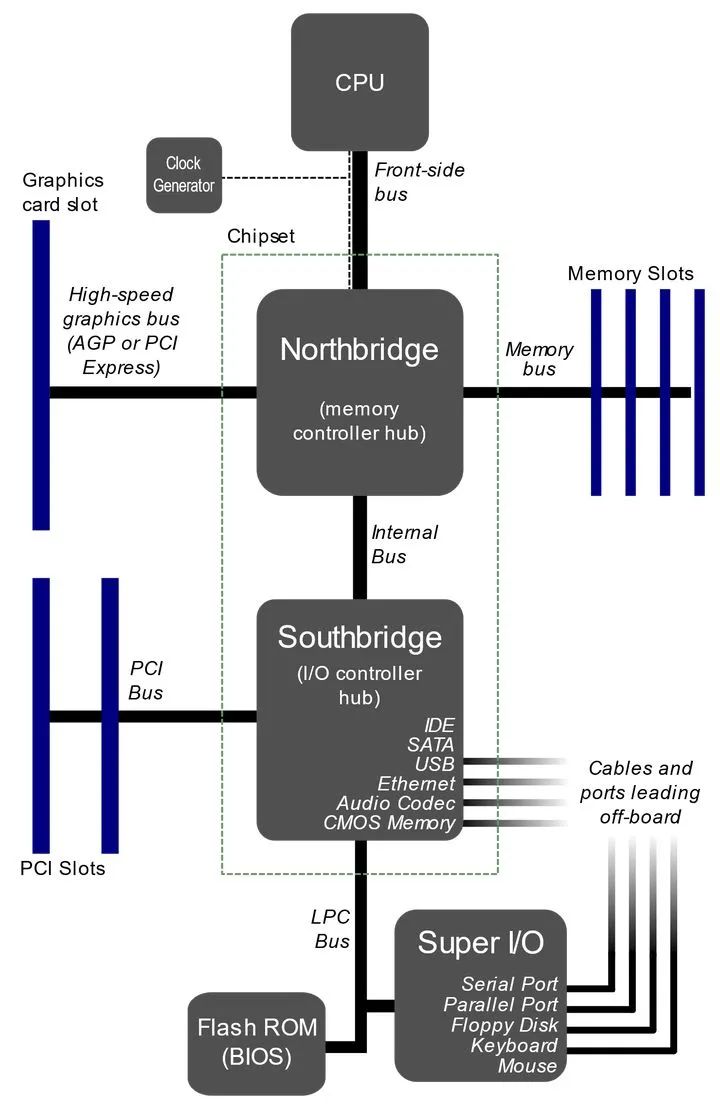

最早在1958年IBM 709、1964年IBM360就有关于IO processor的概念,为通道控制器,也有Data Synchronizer(数据同步器)的说法,我们可以从下图看到最早计算机I/O管理的特点。

每个I/O设备有自己的控制单元,接入总线中,通道控制器相当于一个仲裁模块(后面的发展将有自己的通道指令),接收CPU的指令,执行操作,选择相应的外设。设备都是低速设备,以IBM360为例,IBM 360性能较低的可以每秒执行34500次指令,最高的每秒执行1660万次指令,而同时期的磁盘IBM 2302为156KB/s,更不用说打孔的卡处理器、纸带处理设备了。

这个阶段的I/O重点在于要兼容低速设备,管理多样的I/O设备,由于CPU与I/O设备的速度鸿沟,通过I/O processor释放CPU资源,更好的服务于计算密集型任务。

由于外设速度的两级分化,渐渐形成了南北桥的结构,北桥通过FSB(前端总线)与CPU相连,并与高速外设(内存、显卡)、南桥相连,而南桥则负责与低速外设(键盘、鼠标)相连。南北桥的结构同样起到了一定隔离I/O资源的作用,让CPU更好的服务于计算密集型任务。

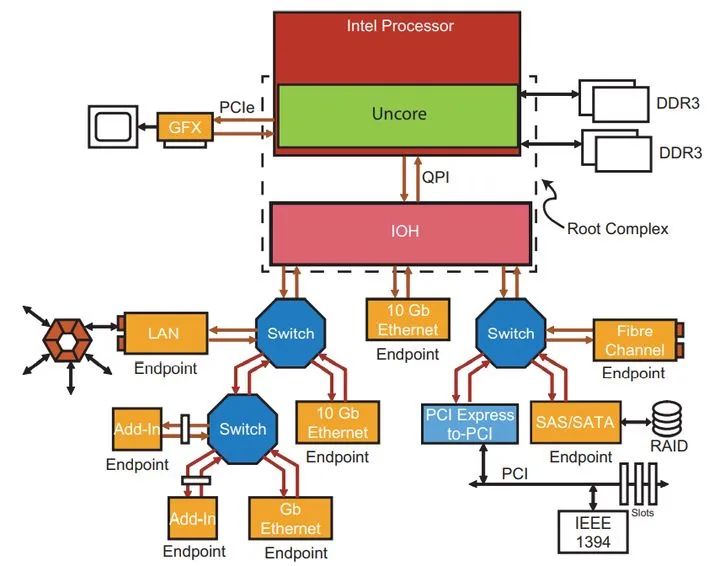

高速总线(PCIe)的出现,南北桥的结构名存实亡,除了DDR内存(并行总线,不包括IBM的串行内存总线方案),所有的外设都可以挂载在PCIe上。但I/O的控制权还在CPU中。如下图所示:

随着网络速度的不断提高,CPU的运行资源在I/O处理中被剥夺了很大一部分且不能满足高速I/O的需求。CPU的运算处于低效率的过程,这在今天仍然是一个问题,这也是DPU作为I/O角色需要解决的问题——高效的I/O平面。

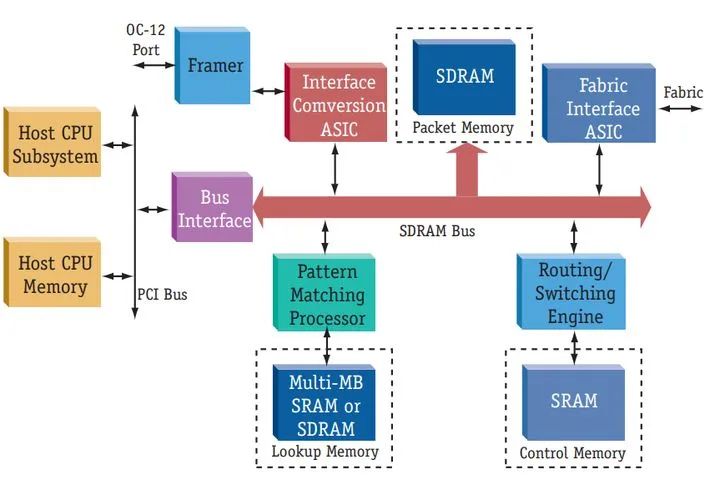

网络处理器,是一种专门应用于网络应用数据包的处理器(ASIC)。由于网络处理的复杂性,通过CPU+NP的结构,能够获得对网络处理的较大提升。

上图是Freescale Semiconductor 2000在“Network Processors: A Definition and Comparison”关于Network Processor的设计。与路由器、交换机的芯片不同,NP需要更多的功能集成、开放的编程接口、提供较高的灵活性等等。但NP却只局限于对网络的处理,发包接包,路由算法的加速,协议规则的加速等等。从下图2010年IBM 的NP,可以看到现在基于FPGA加速的思路。

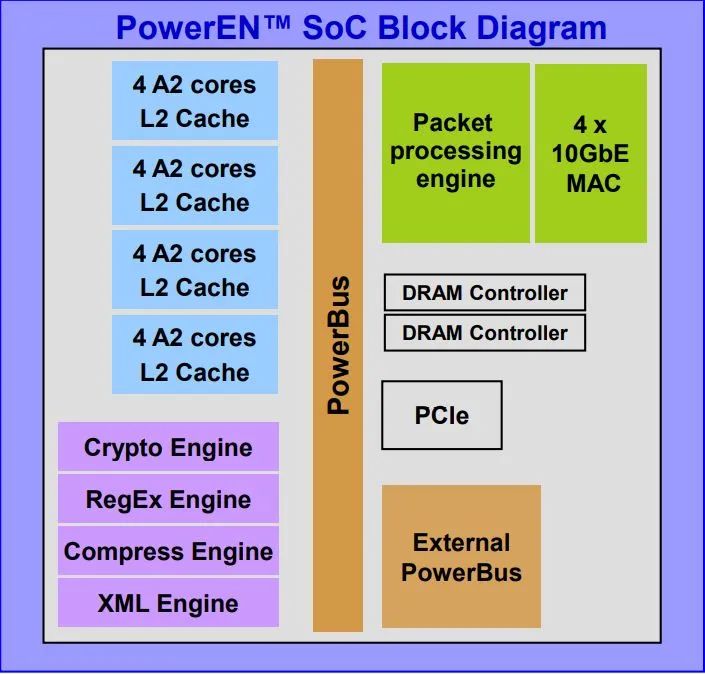

PowerEN不仅提供了网络处理能力——Packet processing engine,同时能看到它的其他加速核心,加密(Crypto Engine)、正则表达式(RegEx Engine)、压缩(Compress Engine)、XML解析(XML Engine)。从通用逐渐向特定的需求优化,从只聚焦网络处理到融合一些基础功能的加速器,这也将是DPU将要承担的功能角色。

通过硬件卸载不同的协议,或者通过利用硬件的流水线对某些算法达到一个很好的加速效果,这是基于FPGA加速的一些思路。DPU需要协议的卸载,也需要对某些常用功能的加速。协议的标准从来都不会停滞不前,常用功能也会随着时间的推移而变化(PowerEN的XML Engine已然不再),需要DPU的软硬件配合,提供更大粒度的调度或者转换。

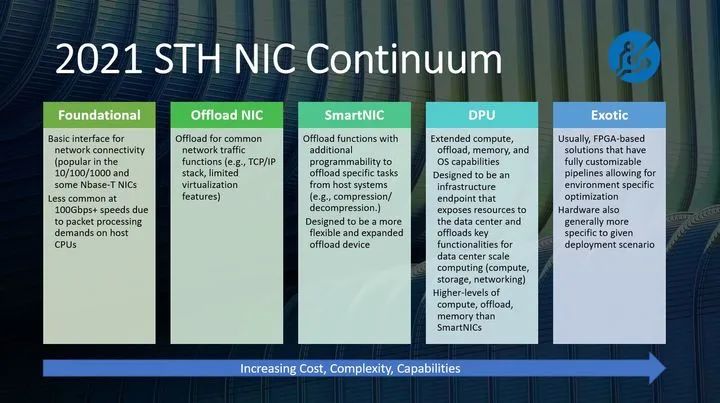

网络是DPU发展的第一推动力,网卡的发展,也将隐藏着DPU的网络功能的发展。下图来自2021 STH NIC Continuum,概述了不同阶段网卡的特点。

从左至右,网卡承担的任务越来越多,复杂性越来越高,但可编程性是面对协议不断变化的必备特征。

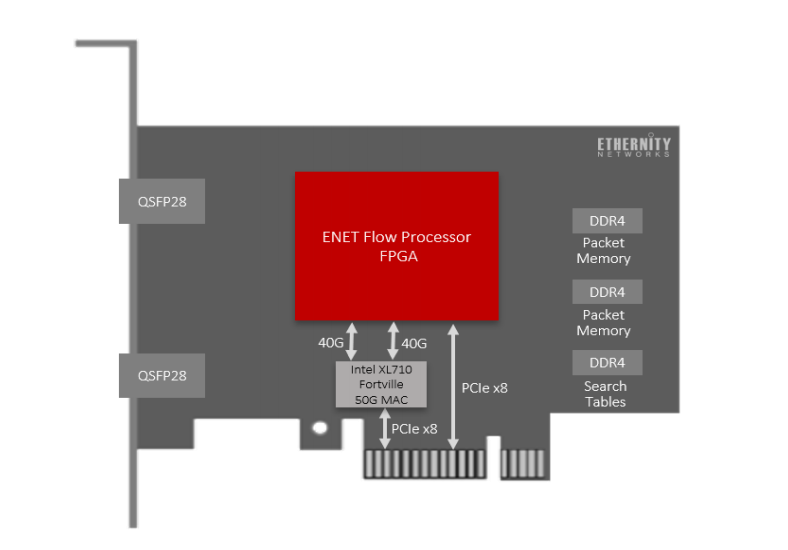

上图是Ethernity基于FPGA的智能网卡。基于FPGA构建智能网卡是提供网络编程灵活性的有效解决方法。DPU继承网卡的功能,就需要具备可编程性,但要新的体系结构去结合不仅网络相关的功能,还有计算、存储等其他功能。

从计算为中心的时代,慢慢转变为以数据为中心的时代。尤其是以数据中心云计算为应用场景,需要对庞大数据的处理能力,CPU由于复杂的软件协议栈,在高速的数据交换处理中根本没有优势,无法承担得起这样的任务。

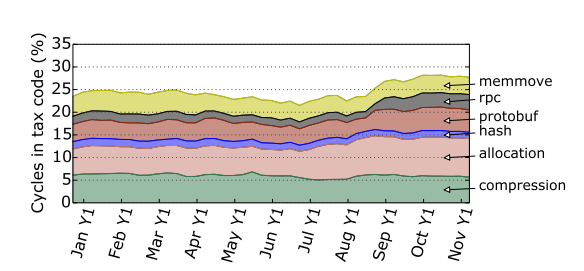

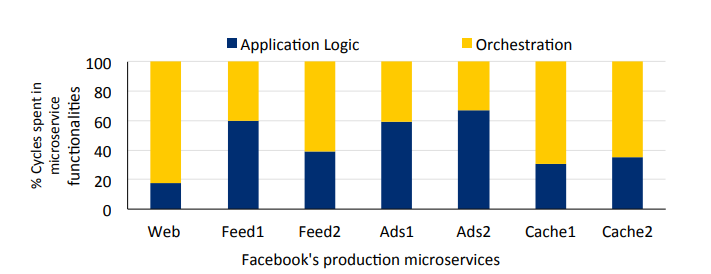

下图是Facebook在2020年关于数据中心加速的研究实验现象,上图是Google在大规模数据集群中的现象。两者的研究都表明22%到80%的CPU周期可能被微服务的通信开销所消耗。而这也是CPU在数据中心表现低效的原因。

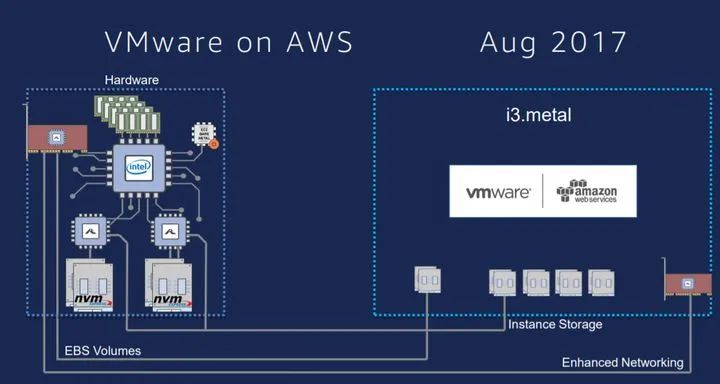

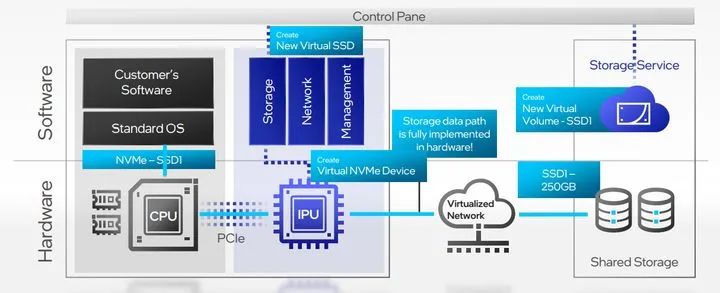

为了减少开销释放CPU性能,工业界不同厂商做了很多尝试,提出了不同的解决方法(XPUs)。Amazon于2016年提出Nitro System,如下图所示。

Nitro System提供了硬件卸载的高速网络、EBS存储、NVMe本地存储、RDMA远程存储、安全控制等功能,通过Nitro Cards和Nitro Security Chip实现,尝试将CPU从繁杂的数据处理中解放出来。

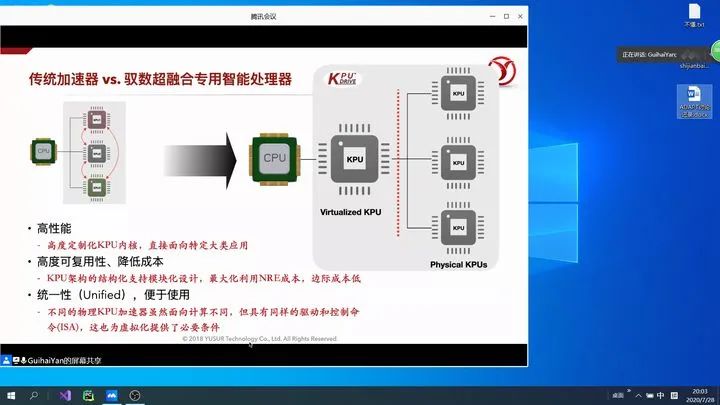

中科驭数提出的KPU,同样是基于这样的尝试,作为CPU的数据处理单元,直接面向大规模数据应用,通过高度定制化KPU核,提供应用加速能力。

从上面的架构图中,我们可以看到KPU试图实现的是高性能、统一性、可复用性,解决CPU数据处理能力不足的问题。

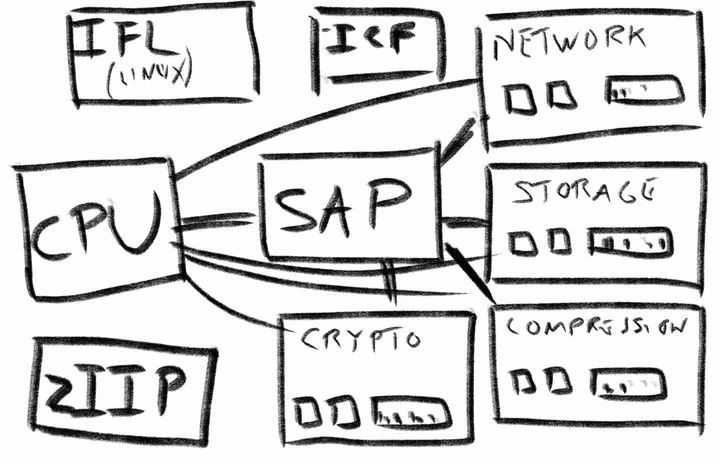

IBM最新的大型机(main frame)——Z15,通过SAP(DPU的位置)将CPU从网络、存储、加密、压缩中释放出来。

也是在这样的情况下,DPU的出现或许将是解决目前问题的关键。

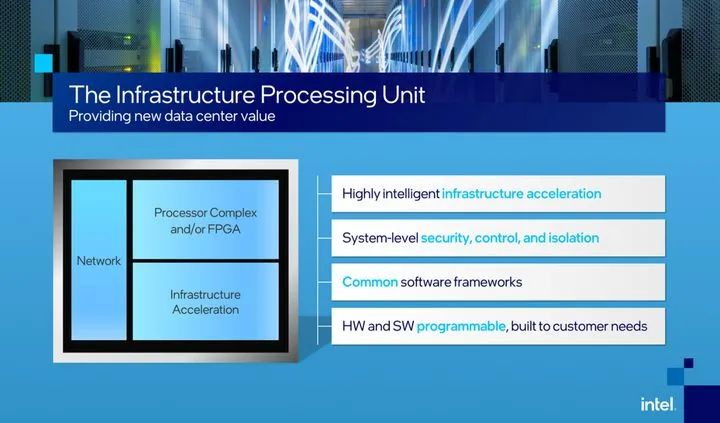

Intel——IPU

在数据中心应用场景中,Intel于2021年6月首次提出IPU(Infrastructure Processing Unit)概念,由于其功能和应用场景与DPU有较大重合,也可以看作是DPU的一种尝试。IPU的定义:Programmable network devices that intelligently manage system-level resources by securely accelerating networking and storage infrastructure functions in a data center。同样是基于功能定义,具有三大特征,安全、存储加速、网络加速。

从上图我们可以看到IPU的功能划分,左侧的Block design,Processor Complex and/or FPGA 提供软硬件可编程性,运行ISP/CSP的特定服务,Infrastructure Acceleration加速存储虚拟化、安全(加解密)、网路虚拟化等负载请求,Network提供高带宽的包处理、包分析等能力。

从上图可以看到,应用IPU之后,数据中心原有的网卡将被IPU代替,这也是DPU在未来重要的应用场景之一。同时通过IPU的基础功能(软件虚拟化——>硬件虚拟化,以及其他的资源管理能力)的卸载,实现资源的隔离与CPU的充分利用。CPU将耗费极少的时间管理资源(通信),而真正专注于用户任务。

Intel Architecture Day 2021为我们揭露了IPU加速的两种路线,一种是基于ASIC的IPU,另一种是基于FPGA的加速。

从上图可以看到,ASIC将提供相比于FPGA更优的安全、网络和存储加速的性能以及较低的功耗。FPGA的加速将适合于不断改进的标准,具有可编程性,更短的TTM(Time to Market),满足可定制需求。

ASIC IPU —— Mount Evans

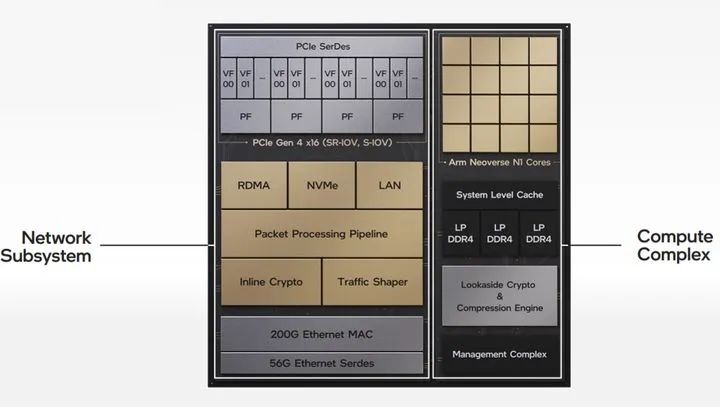

Mount Evans于2021.8月发布,分为两大子系统,网络单元与计算单元,如下图所示:

网络单元

网络单元实现与CPU、各种外设的互连,并提供高效的数据处理能力。最多支持4个物理机(PF)的连接(全双工200Gb/s),实现SR-IOV、S-IOV虚拟化协议(VF)的硬件实现,RDMA(基于ROCEv2),NVMe存储控制协议,IPSec等。

计算单元

计算单元由16个Arm N1核、Cache、加速引擎和管理处理器四部分组成。实现对整个IPU的控制与功能拓展。

IPU的ASIC版本,通过Arm核赋予其通用能力,通过协议的卸载加速基础应用存储、网络,通过软硬件协同设计,通过硬件加速引擎加速压缩、加解密等功能,能够利用DPDK、SPDK和P4,提供一定程度的灵活性。

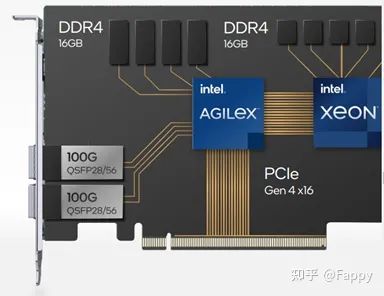

FPGA IPU —— Oak Springs Canyon

Oak Springs Canyon由Agilex FPGA与Xeon-D SoC两部分构成。如下图所示:

Xeon-D SoC 将运行嵌入式Linux,提供足够的灵活性,Agilex FPGA将提供可编程性,根据应用场景,专用加速CSP/ISP所需要的功能,提供高性能的数据处理。

Fungible —— F1、S1

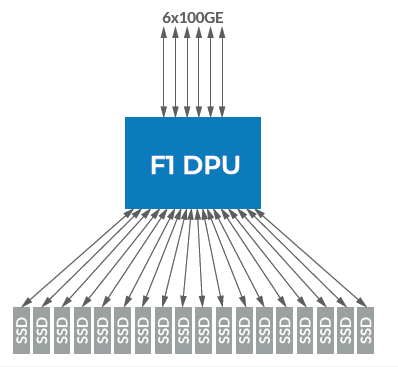

Fungible有两款DPU芯片,专注于网卡的S1与面向服务器端业务的F1。

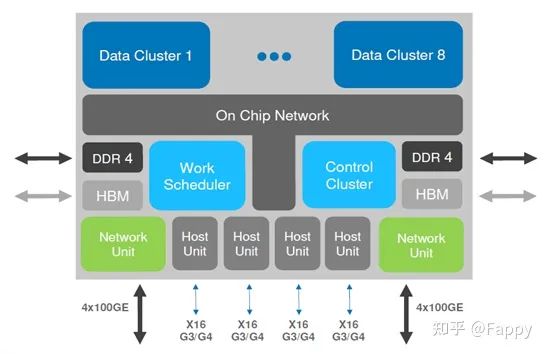

F1硬件架构如下:

数据集群(Data Cluster),每个集群中六核四线程,一共192个线程加速数据移动、数据保护、数据分析。

控制集群(Control Cluster)运行Linux系统,负责安全认证,加速不同加密算法(RSA等)。

网络单元(Network Unit),实现低延迟以太网、P4语言支持、包加密、与数据集群的紧耦合以及精确的时间控制。

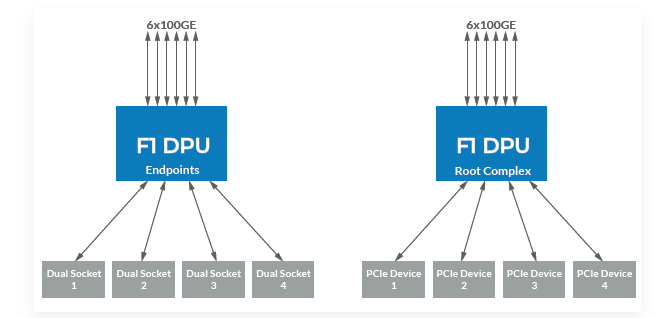

F1将扮演三个角

16个独立全双工的控制器; X86或Arm架构CPU的端设备; PCIe可拓展的RC。

DPU的诞生,是目前计算机冯诺伊曼架构造成的巨大瓶颈——存储程序、指令驱动可以解决一切问题,但并不是对所有程序应用在这种架构中能获得最大的处理能力。DPU的未来可能是在架构上的创新弥补当前架构的不足。

原文链接:

https://zhuanlan.zhihu.com/p/402706136

下载链接:

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

推荐阅读

更多架构相关技术知识总结请参考“架构师全店铺技术资料打包”相关电子书(37本技术资料打包汇总详情可通过“阅读原文”获取)。

全店内容持续更新,现下单“全店铺技术资料打包(全)”,后续可享全店内容更新“免费”赠阅,价格仅收198元(原总价350元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“架构师技术全店资料打包汇总(全)”电子书资料详情。