来源:Hardware Info

编辑:Priscilla

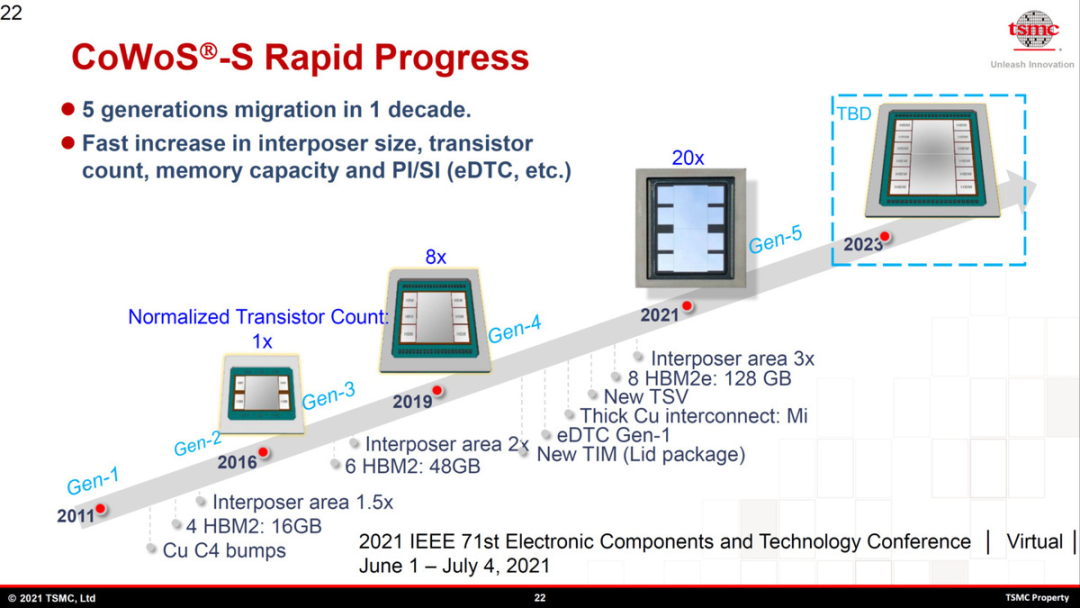

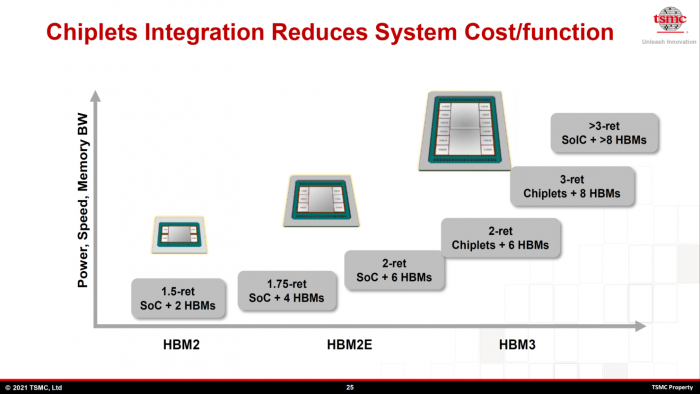

【新智元导读】近日,Hot Chip 33大会在线上举行,台积电在会上介绍了自家封装技术路线图。第5代CoWoS封装技术将于今年晚些时候问世,拥有8个HBM2e堆栈的空间,容量高达128 GB,比第3代技术多存储20倍晶体管,预计2023年发布第6代CoWoS。

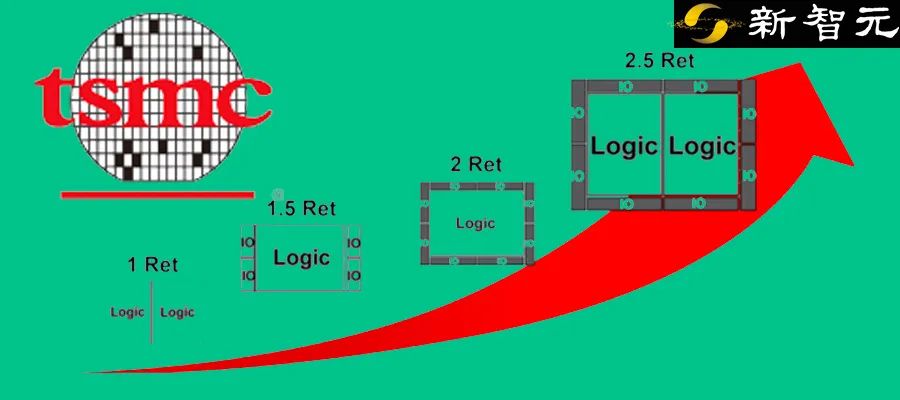

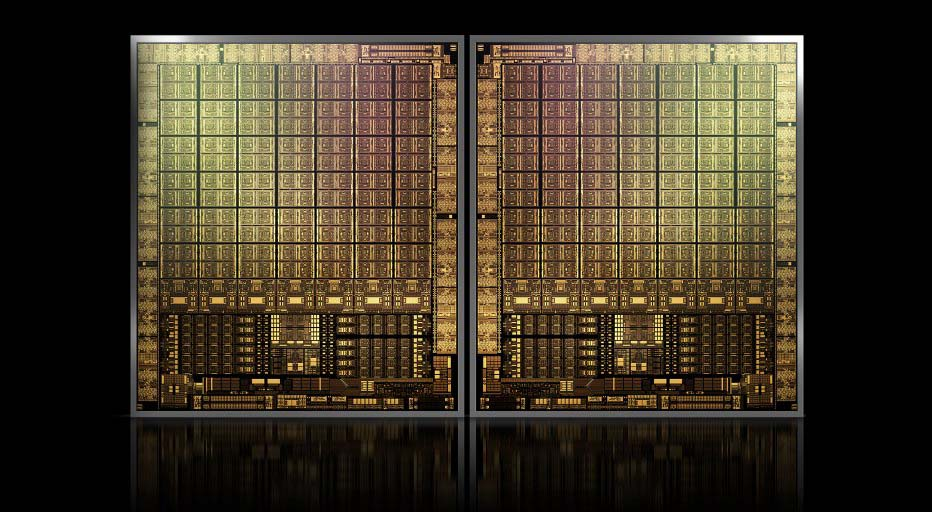

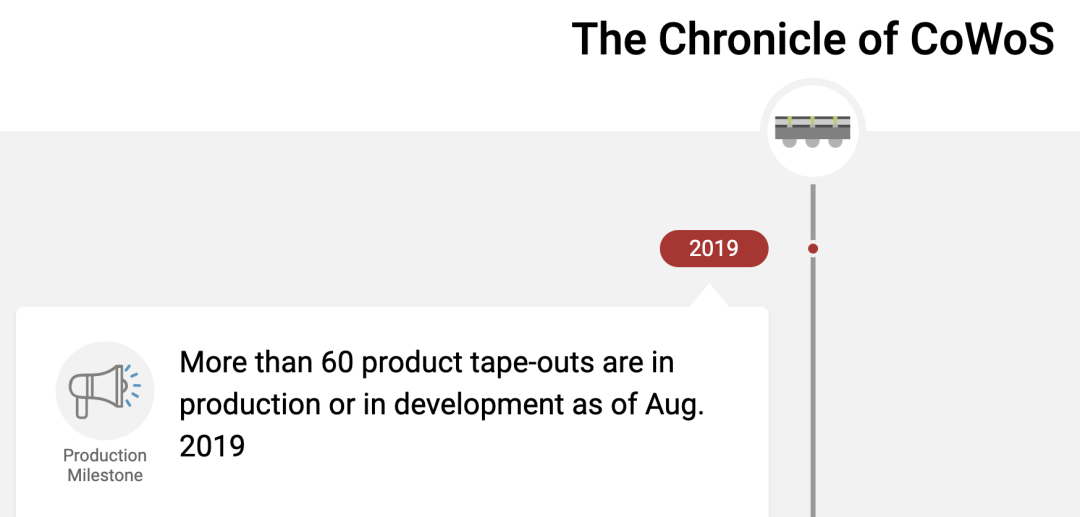

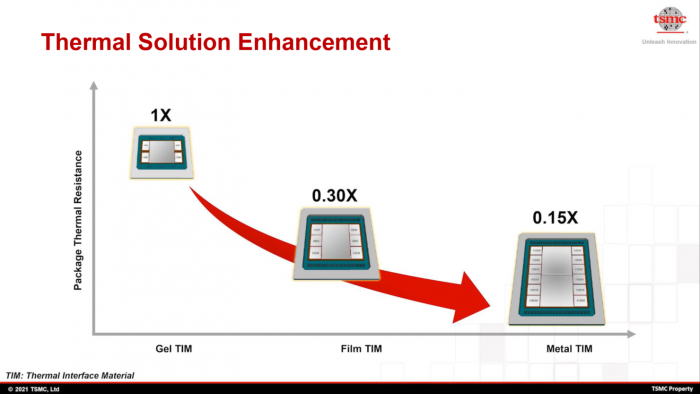

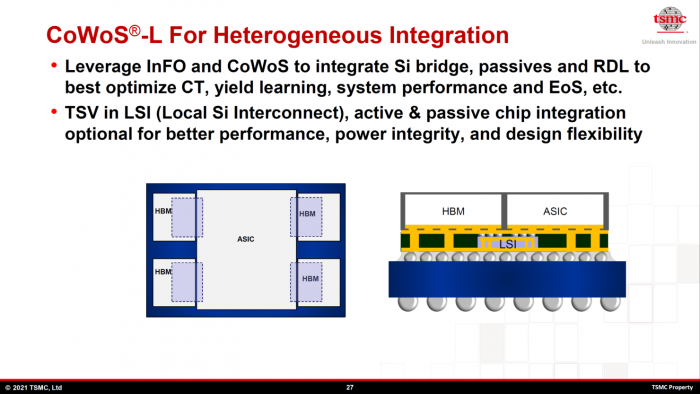

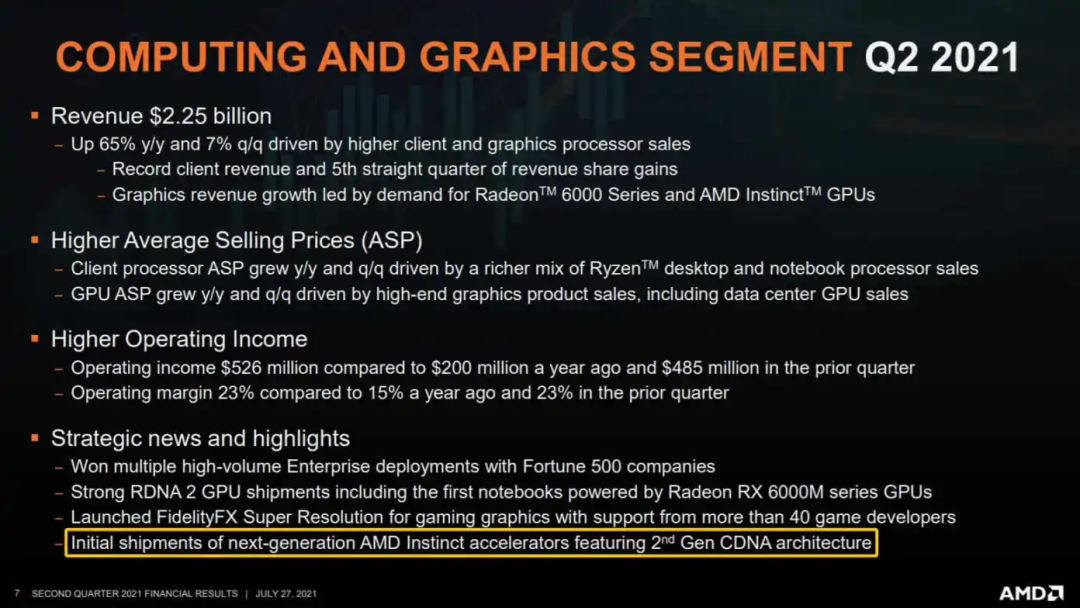

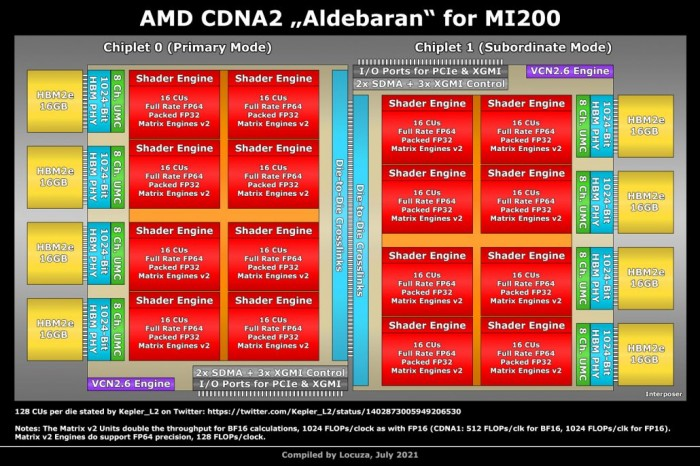

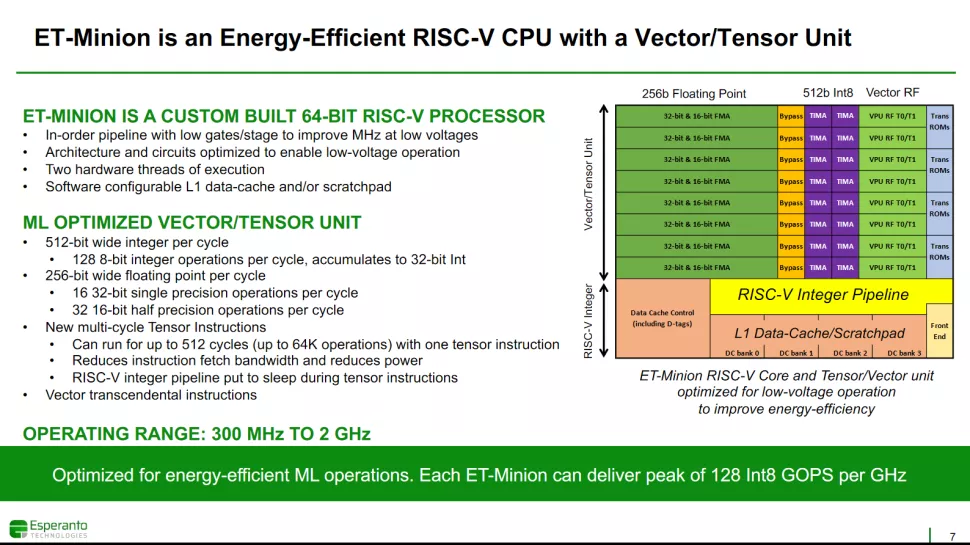

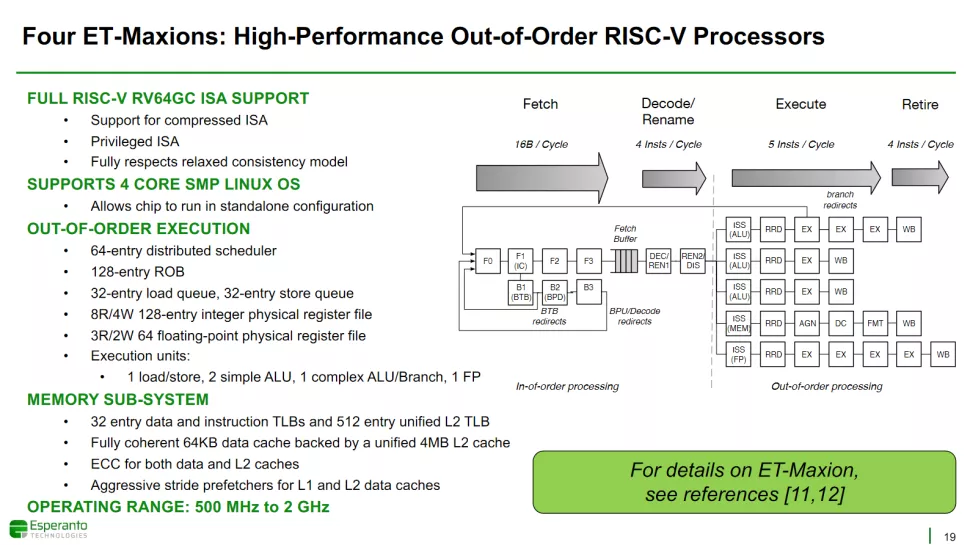

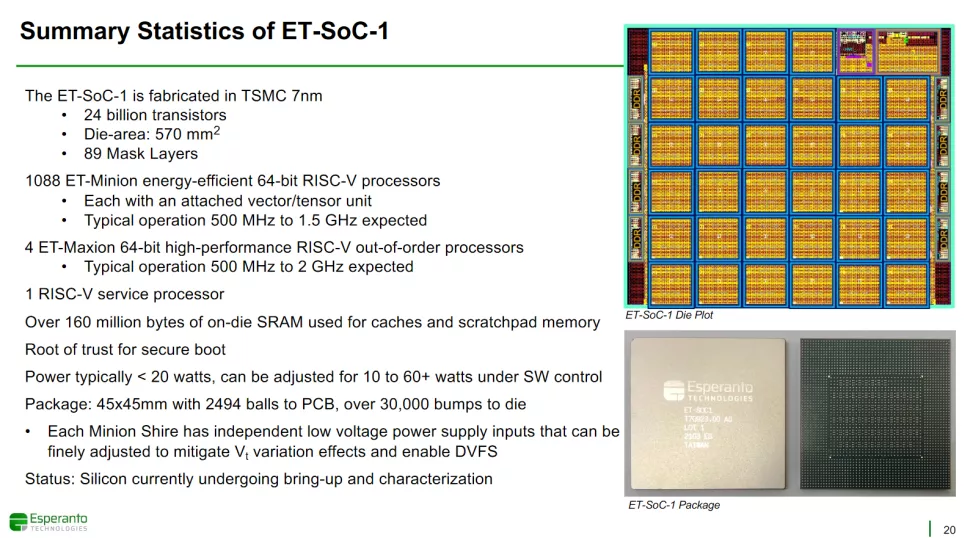

台积电介绍最先进的封装技术路线图:存储的晶体管再多20倍!近日,台积电在Hot Chips 33大会上宣布推出「2.5D」晶片技术。第五代CoWoS封装技术将在今年晚些时候问世,与第三代封装技术相比,有望能够多存储20倍晶体管。台积电的半导体技术在业内遥遥领先,在先进芯片封装技术方面同样取得了快速进展。过去十年,台积电已经推出五代不同的基板上芯片封装工艺,涵盖了消费级与服务器芯片领域。自2011年来,台积电就发布了第一代各部件的堆叠。截至2019年8月,台积电CoWoS已经有60多种产品流片正在生产或开发中。最新一代封装技术的目标总结为四个字:节省空间,也就是在一个封装中处理尽可能多的芯片。新封装技术增加3倍多中介层面积,有8个HBM2e堆栈的空间,容量高达128 GB。此外,新封装技术还使用了全新的硅通孔(TSV)解决方案,实现厚CU互连。初代CoWoS封装技术是基于凝胶的热风化(Gel TIM),与之相比,台积电提供了最新的SOC散热解决方案。以Metal TIM的形式,将封装热阻降低到初代的0.15倍。台积电的第六代CoWoS封装技术预计将在2023年发布。目前对于第六代技术知之甚少,只能确定第六代技术将会在同一封装内容纳多达8组HBM3内存和2组计算芯片。目前最让人期待的就是台积电第5代CoWoS封装工艺在AMD MI200 Aldebaran GPU上的应用。AMD在第2季度财报中就披露了MI200 Aldebaran GPU的初始出货量。MI200 Aldebaran GPU拥有第二代CDNA架构,率先用上了多芯片(MCM)GPU核心设计,超过16000个内核,能提供高达256个计算单元(CU)和128GB的HBM2E缓存。内部分为主、副两个芯片,两者都由8个着色器(SE)组成,共计16个SE。每个芯片拥有128 CU/8192个流处理器,总计256 CU/16384个流处理器,辅以新的XGMI互联设计,且每个小芯片都具有VCN 2.6引擎/主IO控制器。作为首款用上MCM GPU设计的芯片,Instinct MI200将直接对标英特尔7nm Ponte Vecchio和英伟达Ampere新品。此外,英伟达的Hopper GPU也使用了MCM小芯片架构,同样可能会交由台积电代工,预计将在2022年上市。AMD CNDA 3(MI300)和英伟达Ampere的下下一代,都有望采用台积电的N3工艺节点。Esperanto Technologies是一家旧金山的初创公司,同样参加了今年的HotChips 33展示会。该公司在会上展示了代号为「ET-SoC-1」的最新处理器,是首批千核处理器之一。这个处理器有1088个更小尺寸、低功耗的ET-Minion 64位RISC-V内核,可以并行运行,轻松执行工作负载,希望成为最高性能的商用RISC-V芯片。为了满足大型数据中心高性能、低功耗的要求,Esperanto芯片用低于20瓦的功率运行,适应系统功率限制。是一种通用的并行处理解决方案,可以加速许多可并行化的工作负载。为了配合小内核,Esperanto封装了额外4个高性能ET-Maxion 64位RISC-V 内核。较小的内核是按顺序执行设计,而较大的内核是为乱序执行设计的。整个芯片在台积电的工厂中使用7nm制造节点进行流片。ET-SoC-1设计了超过1.6亿字节的片上SRAM,分为L1缓存和暂存器存储器。它支持PCIe Gen4、256位宽(四通道)LPDDR4x内存,并具有用于安全启动、系统管理和计时器的 RISC-V 服务处理器。所有这些都封装在一个570平方毫米的芯片中,其中包含225亿个晶体管。在常规操作中,它的使用功率低于20瓦,可以针对10-60瓦的工作负载进行软件配置。

参考资料:

https://www.esperanto.ai/esperanto-technologies-unveils-energy-efficient-risc-v-based-machine-learning-accelerator-chip-at-hot-chips-33-conference/

https://nl.hardware.info/nieuws/78166/hot-chips-tsmc-stopt-20-keer-zoveel-transistoren-in-de-nieuwste-generatie-cowos