ASIC芯片技术和知识介绍

ASIC (Application Specific Integrated Circuit )芯片是专用集成电路,是针对用户对特定电子系统的需求,从根级设计、制造的专有应用程序芯片,其计算能力和计算效率可根据算法需要进行定制,是固定算法最优化设计的产物。ASIC 芯片模块可广泛应用于人工智能设备、虚拟货币挖矿设备、耗材打印设备、军事国防设备等智慧终端。

在硬件层面,ASIC 芯片由基本硅材料、磷化镓、砷化镓、氮化镓等材料构成。在物理结构层面,ASIC 芯片模块由外挂存储单元、电源管理器、音频画面处理器、网络电路等IP核拼凑而成。同一芯片模组可搭载一个或几个功能相同或不同的ASIC 芯片,以满足一种或多种特定需求

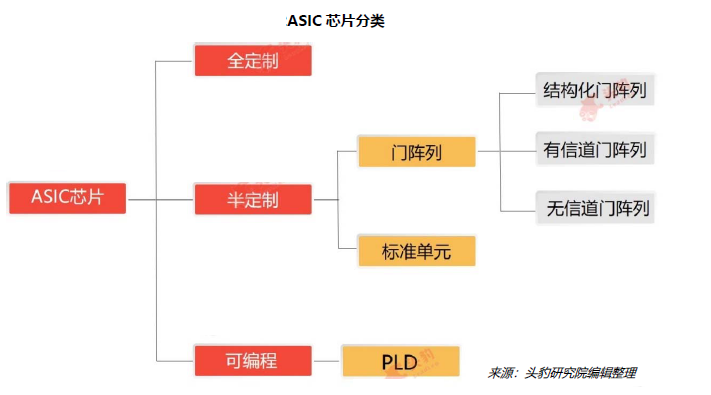

(1) 根据定制程度不同,ASIC 芯片可被分为全定制ASIC 芯片、半定制ASIC 芯片及可编程ASIC芯片

全定制ASIC 芯片是定制程度最高的芯片之一,研发人员基于不同电路结构设计针对不同功能的逻辑单元,于芯片板搭建模拟电路、存储单元、机械结构。逻辑单元之间由掩模版连接,ASIC 芯片掩模版也具备高度定制化特点。

全定制化ASIC 芯片设计成本较高,平均每单位芯片模块设计时间超过9 周。该类芯片通常用于高级应用程序。

相对半定制化ASIC 芯片,全定制化ASIC 芯片在性能、功耗等方面表现优秀。如应对相同功能,在同种工艺前提下,全定制化ASIC 芯片平均算力输出约为半定制化ASIC 芯片平均算力输出的8 倍,采用24 纳米制程的全定制化ASIC 芯片在性能上优于采用5 纳米制程的半定制化ASIC 芯片。

构成半定制ASIC 芯片的逻辑单元大部分取自标准逻辑单元库,部分根据特定需求做自定义设计。相对全定制ASIC 芯片设计成本较低,灵活度较高。

门阵列ASIC 芯片包括有信道门阵列、无信道门阵列和结构化门阵列。门阵列ASIC 芯片结构中硅晶片上预定晶体管位置不可改变,设计人员多通过改变芯片底端金属层等方式调整逻辑单元互连结构。

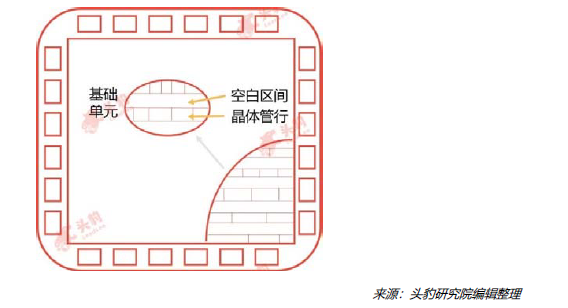

有信道门阵列ASIC 芯片:该类芯片晶体管位置高度固定,设计人员可在晶体管行之间预定义的空白空间进行电路布局;

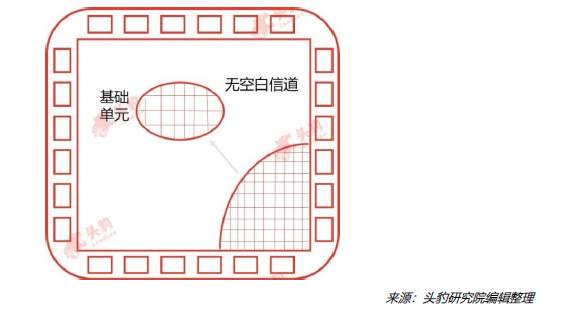

无信道门阵列ASIC 芯片:无信道结构下,晶体管行之间不存在电路布局空间,设计人员通常于门阵列单元上方进行布线;

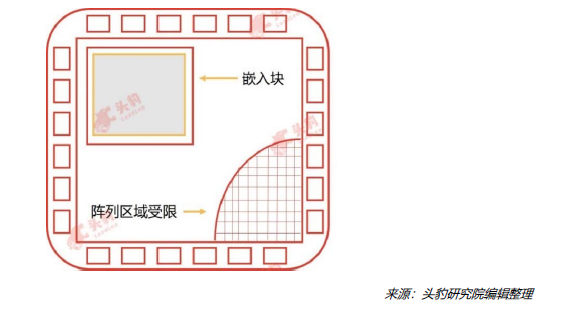

结构化门阵列ASIC 芯片:该结构包括基本门阵列行及嵌入块。嵌入块可提高线路布局灵活度,但对芯片体积构成限制。该结构下,线路布局面积使用效率较高,设计成本较低,周转时间较短。

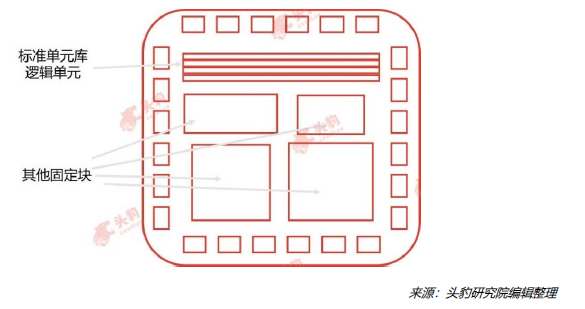

b、 标准单元

该类ASIC 芯片由选自标准单元库的逻辑单元构成。设计人员可按算法需求自行布置标准单元。除标准单元外,微控制器、微处理器等固定块也可用于标准单元ASIC 芯片架构。

③ 可编程ASIC 芯片

广义而言,可编程ASIC 芯片可分为FPGA 芯片和PLD 芯片。在实际生产过程中,将FPGA 芯片列为不同于ASIC 芯片的研究机构和企业数量不断增加,故本报告仅将PLD(Programmable Logic Device)视为可编程ASIC 芯片子类别。

PLD 亦称可编程逻辑器件,在结构上包括基础逻辑单元矩阵、触发器、锁存器等,其互连部分作为单个模块存在。设计人员通过对PLD 进行编程以满足部分定制应用程序需求。

① TPU 为张量处理器,专用于机器学习。如Google 于2016 年5 月研发针对

Tensorflow 平台的可编程AI 加速器,其内部指令集在Tensorflow 程序变化或更新算法时可运行。

② BPU 是大脑处理器,是由地平线科技提出的嵌入式人工智能处理器架构。

③ NPU 是神经网络处理器,在电路层模拟人类神经元和突触,并用深度学习指令集直接处理大规模电子神经元和突触数据。

CPU 等传统芯片通过读取、执行外部程序代码指令而生成结果,相对而言,ASIC 芯片读取原始输入数据信号,并经内部逻辑电路运算后直接生成输出信号。

相对CPU、GPU、FPGA 等类型芯片,ASIC 芯片在专用系统应用方面具备多元优势,具体表现在如下几方面。

① 面积优势:ASIC 芯片在设计时避免冗余逻辑单元、处理单元、寄存器、存储单元等架构,以纯粹数字逻辑电路形式构建,有利于缩小芯片面积。应对小面积芯片,同等规格晶圆可被切割出更多数量芯片,有助于企业降低晶圆成本。

② 能耗优势:ASIC 芯片单位算力能耗相对CPU、GPU、FPGA 较低,如GPU 每算力平均约消耗0.4 瓦电力,ASIC 单位算力平均消耗约0.2 瓦电力,更能满足新型智能家电对能耗的限制。

③ 集成优势:因采用定制化设计,ASIC 芯片系统、电路、工艺高度一体化,有助于客户获得高性能集成电路。

④ 价格优势:受到体积小、运行速度高、功耗低等特点影响,ASIC 芯片价格远低于CPU、GPU、FPGA 芯片。当前全球市场ASIC 芯片平均价格约为3 美元,远期若达到量产规模,ASIC 芯片价格有望保持持续下降态势。

① ASIC 芯片定制化程度较高,设计开发周期长,成品需要做物理设计和可靠性验证,面市时间较慢。

② ASIC 芯片对算法依赖性较高。人工智能算法高速更新迭代,导致ASIC 芯片更新频率较高。

③ 因ASIC 芯片定制化程度较高,研发周期相对漫长,扩大了ASIC 成品被市场淘汰的风险。

① 谷歌于2016 年推出TPU,谷歌旗下2017 版AlphaGo 物理处理器中镶嵌4 个TPU,可支持谷歌云TPU 平台和机器学习超级计算机。

② IBM 通过模拟大脑结构于2014 年8 月推出制程为28 纳米的第二代TrueNorth芯片,可应用于实时视频处理。

③ 英特尔于2017 年推出Xeon 系列ASIC 芯片。该系列芯片可独立充当处理器,无需附加主机处理器和辅助处理器,可应用于机器深度学习。

④ 斯坦福大学推出基于新神经形态计算架构的ASIC 芯片运算速度为普通电脑9,000倍,可模拟约100 万个大脑神经元、几十亿个突触连接。

⑤ 新兴科创企业将ASIC 芯片应用拓展至安防、辅助驾驶、传统家电、智慧医疗等领域。

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

推荐阅读

更多架构相关技术知识总结请参考“架构师技术全联盟书店”相关电子书(35本技术资料打包汇总详情可通过“阅读原文”获取)。

全店内容持续更新,现下单“架构师技术全店打包汇总(全)”,后续可享全店内容更新“免费”赠阅,价格仅收188元(原总价290元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“架构师技术全店资料打包汇总(全)”电子书资料详情。