编辑:好困

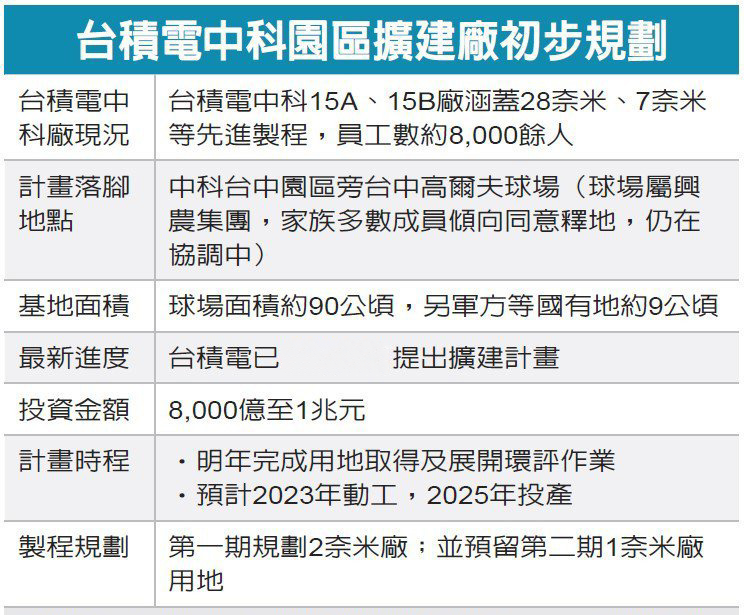

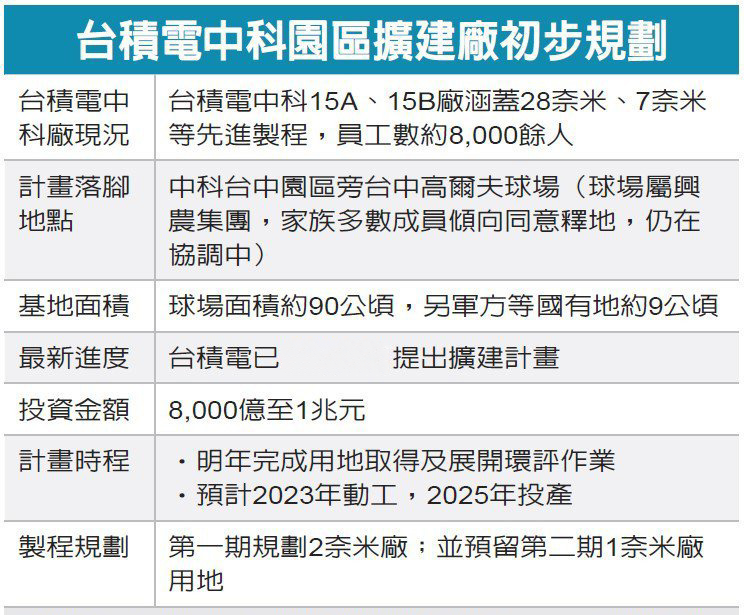

【新智元导读】台积电即将斥资近1万亿新台币,在中科园区附近的高尔夫球场兴建2nm晶圆厂,并为后续1nm工厂预留用地。

近日,台积电正式提出2nm以及后续1nm的工厂扩建计画。预计总投资金额将高达8000亿至1万亿新台币(约1840-2300亿元),占地近100万平方米。据联合新闻网报道,位于中部科学园区(中科)的新工厂将占用周边的一个高尔夫球场以及部分公有土地。这也是继竹科宝山之后,台积电规划的第二个2nm晶圆厂。业界指出,相较于后续用地问题仍待解决的台积电竹科宝山2nm工厂,台中高尔夫球场土地所有权单纯,一旦与兴农集团完成协商,很有可能超过竹科宝山建厂进度。根据台积电初步规划,工厂预计在明年获得用地许可并展开环境影响评估,最快于2023年动工,预计可创造约8000个就业机会。这两年由于对芯片需求的剧增,台积电产能扩充与开发较往年可说是「五倍速」前进。为了确保产能的提升,相关的支出也大举拉高,尤其是在先进制程方面。目前台积电在中科的制程涵盖28nm及7nm,由于2nm及1nm制程的设备可以共用,未来将由1.8nm、1.4nm,逐步向1nm推进。业界推测,台积电2nm最快可以在2024年试产,于2025年实现量产,之后再进入1nm,以及后续的「埃米」制程。工厂建成后预计每年用电量可以达到75万千瓦,当地一个发电机组每年的发电量是55万千瓦。也就是说,全年需要差不多1.5台机组保障台积电新工厂的用电需求。而当地目前总共就只有10台发电机组。

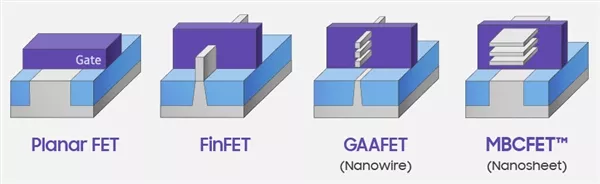

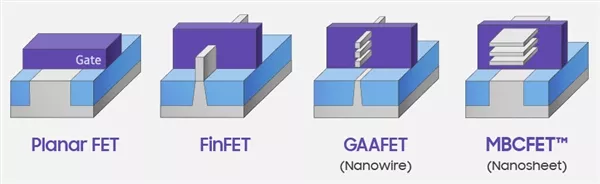

在工艺下降到5nm之前,FinFET(鳍式场效应晶体管)一直是很好的。当达到原子水平 (3nm是25个硅原子排成一行) 时 ,FinFET开始出现漏电现象,可能不再适用于更进一步的工艺水平。

在2nm工艺上,台积电并没有直接使用三星规划在3nm工艺上使用的GAAFET (环绕栅极场效应晶体管),也就是纳米线(nanowire),而是将其拓展成为MBCFET(多桥通道场效应晶体管),也就是纳米片(nanosheet)。

GAAFET是一个周围都是门的场效应管。根据不同的设计,全面栅极场效应管可以有两个或四个有效栅极。通过在栅极上施加电压,你可以控制源极和漏极之间的电流,将其从0切换到1,并创建一个处理器的二进制逻辑。

从GAAFET到MBCFET,从nm线到nm片,可以视为从二维到三维的跃进,能够大大改进电路控制,降低漏电率。

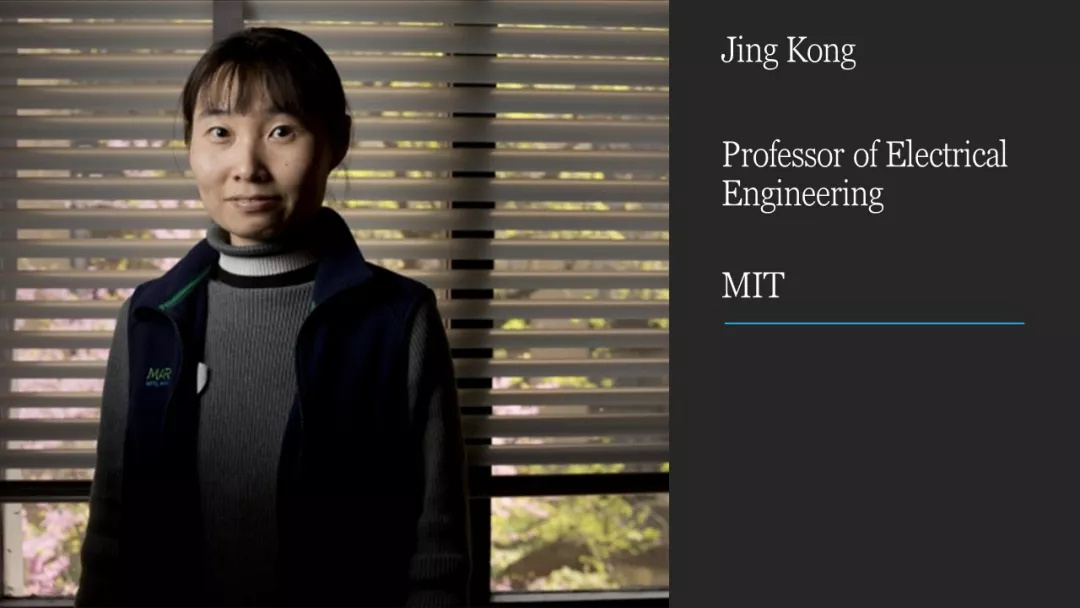

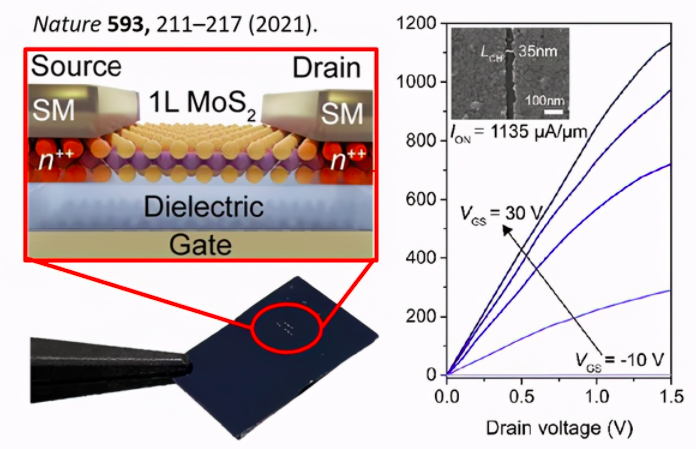

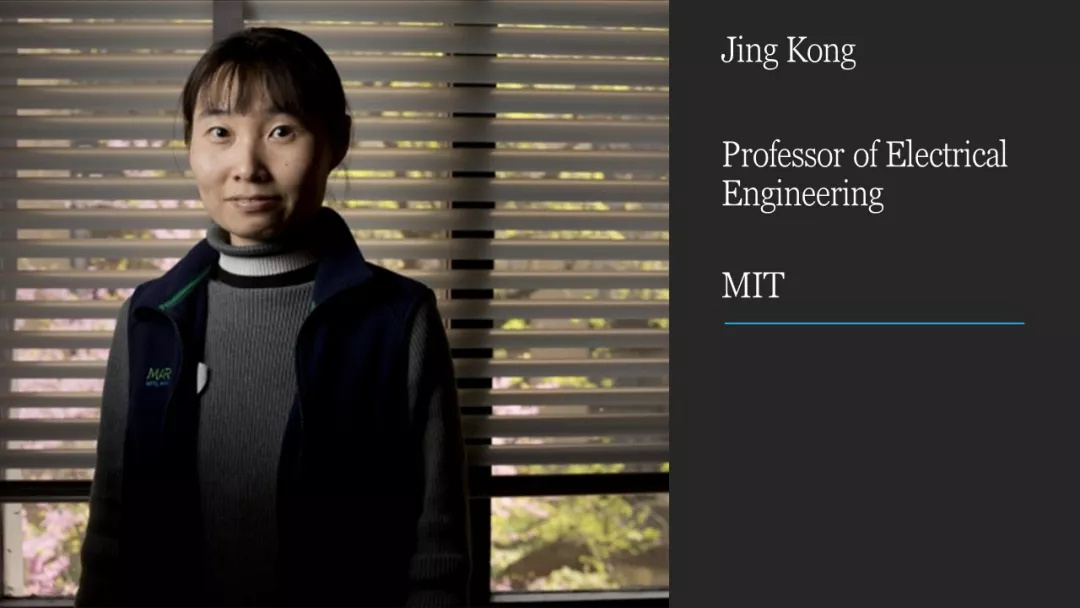

2nm采用以环绕闸极(GAA)制程为基础的MBCFET架构,可以解决FinFET因制程微缩产生电流控制漏电的物理极限问题。今年5月,麻省理工学院(MIT)的孔静教授领导的国际联合攻关团队探索了一个新的方向:使用原子级薄材料铋(Bi)代替硅,有效地将这些2D材料连接到其他芯片元件上。

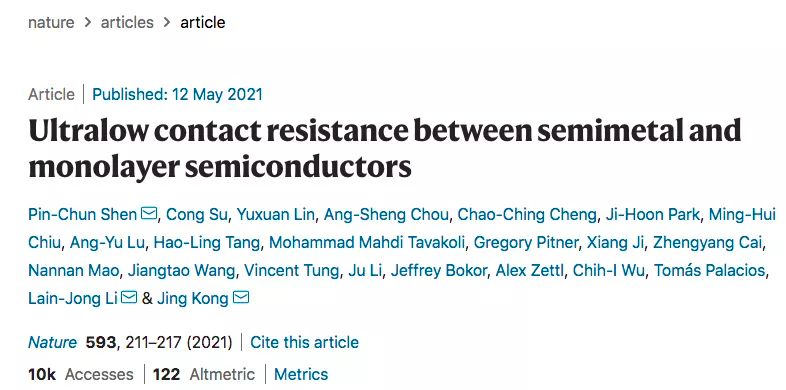

这项研究「Ultralow contact resistance between semimetal and monolayer semiconductors」已发表在Nature期刊上。

论文地址:https://www.nature.com/articles/s41586-021-03472-9

自2019年起,MIT、台大和台积电就展开了漫长的跨国合作。

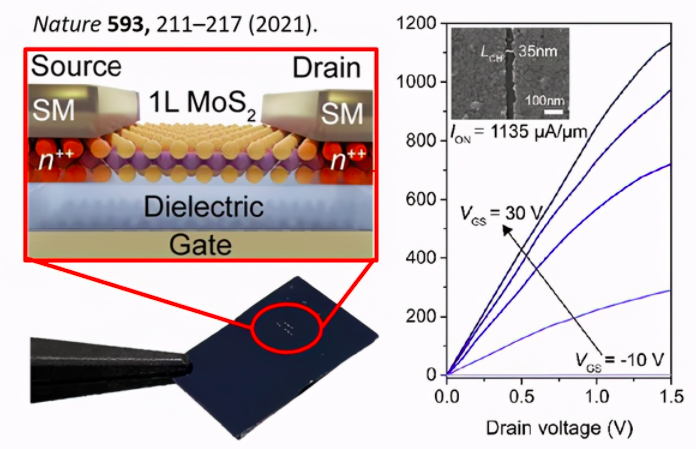

MIT团队最先发现,在「二维材料」上搭配「半金属铋(Bi)」的电极,能大幅降低电阻并提高传输电流。

之后,台积电技术研究部门则将「铋(Bi)沉积制程」进行优化。

最后,台大团队运用「氦离子束微影系统」将元件通道成功缩小至nm尺寸,终于获得突破性的研究成果。

这种材料被作为二维材料的接触电极,可以大幅度降低电阻并且提升电流,从而使其能效和硅一样,实现未来半导体1nm工艺的新制程。

未来,「原子级」薄材料是硅基晶体管的一种有前途的替代品。

研究人员表示,他们解决了半导体设备小型化的最大问题之一,即金属电极和单层半导体材料之间的接触电阻,该解决方案被证明非常简单,

即使用一种半金属,即铋元素(Bi),来代替普通金属与单层材料连接。

这种超薄单层材料,在这种情况下是二硫化钼,被认为是绕过硅基晶体管技术现在遇到的小型化限制的主要竞争者。

金属和半导体材料(包括这些单层半导体)之间的界面产生了一种叫做金属诱导的间隙(MIGS)状态现象,这导致了肖特基屏障的形成,这种现象抑制了电荷载体的流动。

使用一种半金属,其电子特性介于金属和半导体之间,再加上两种材料之间适当的能量排列,结果是消除了这个问题。研究人员通过这项技术,展示了具有非凡性能的微型化晶体管,满足了未来晶体管和微芯片技术路线图的要求。

参考资料:

https://udn.com/news/story/7240/5992392

下载APP

下载APP