统一Chiplet互联标准!英特尔/AMD/Arm/台积电等十大巨头成立UCIe联盟

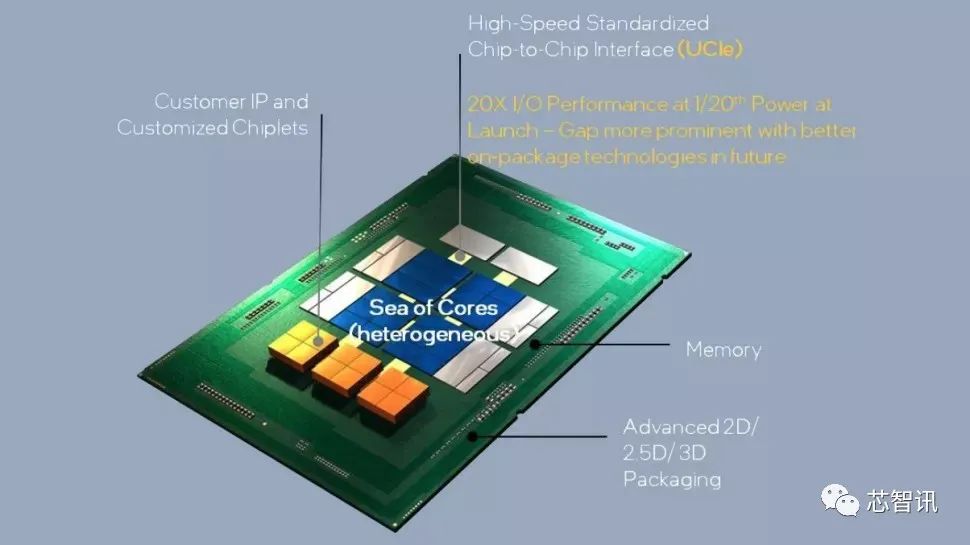

当地时间3月2日,英特尔、AMD、Arm、高通、台积电、三星、日月光、Google云、Meta(Facebook)、微软等十大行业巨头成立了Chiplet标准联盟,正式推出了通用Chiplet(芯粒)的高速互联标准“Universal Chiplet Interconnect Express”,简称“UCIe”,旨在定义一个开放的、可互操作的标准,用于将多个硅芯片(或芯粒)通过先进封装的形式组合到一个封装中。

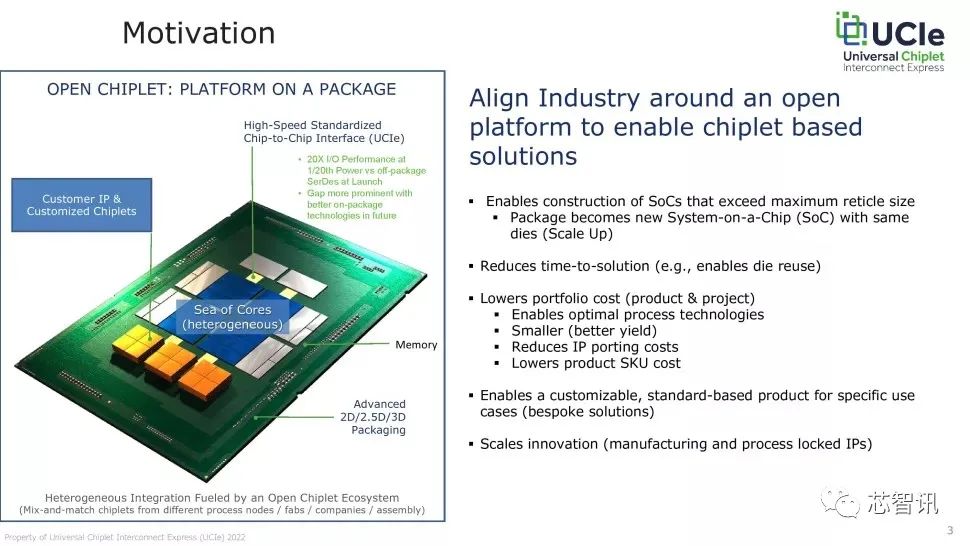

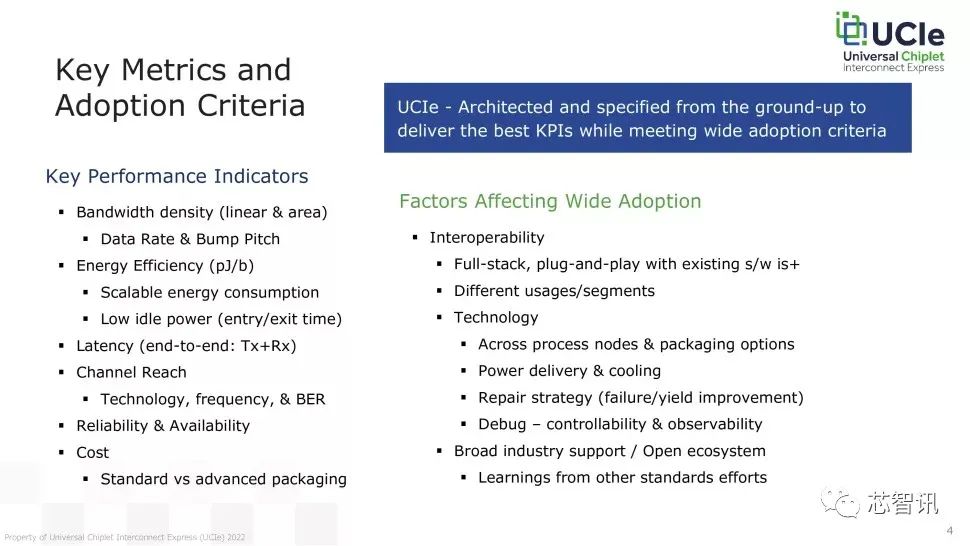

UCIe 标准旨在与其他连接标准(如 USB、PCIe 和 NVMe)一样普遍,同时为Chiplet连接提供卓越的功率和性能指标,降低IP移植及产品SKU数量提升的成本,加速Chiplet设计的创新。

值得注意的是,台积电、三星、英特尔这三个全球领先的晶圆代工厂都将支持这项技术,并且还包括了x86和Arm两大最主流的处理器生态系统。不过可惜的是,目前RISC-V 和 Nvidia并未加入对于该标准的支持。

什么是Chiplet?

随着半导体工艺制程的持续向3nm/2nm推进,晶体管的尺寸已经越来越逼近物理极限,所耗费的时间及成本越来越高,同时所能够带来的“经济效益”的也越来越有限,“摩尔定律”已趋于失效。在此背景之下,Chiplet与先进封装技术被业界寄予厚望,希望能够从另一个维度来延续摩尔定律的“经济效益”。

目前,主流系统级单芯片(SoC)都是将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆上。比如,目前旗舰级的智能手机的SoC芯片上,基本都集成了CPU、GPU、DSP、ISP、NPU、Modem等众多的不同功能的计算单元,以及诸多的接口IP,其追求的是高度的集成化,利用先进制程对于所有的单元进行全面的提升。

而“Chiplet”则是反其道而行之,它是将原本一块复杂的SoC芯片,从设计时就先按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将各个单元彼此互联,最终集成封装为一个系统级芯片组。

简单来说,Chiplet的主要优势在于,可以大幅提高大型芯片的良率,大幅降低设计的复杂度,大幅降低设计成本和制造成本。

近年来,英特尔、AMD、赛灵思等大型芯片厂商都有开始在其相关产品当中采用Chiplet架构。

为什么需要统一的Chiplet互联标准?

芯智讯曾在《后摩尔时代的“助推剂”:Chiplet到底有何优势,挑战又有哪些?》一文当中,详细的介绍了Chiplet与先进封装技术。同时也介绍了,Chiplet所面临的挑战,其中就有特别提到“Chiplet之间的互联标准”问题。

因为,Chiplet(芯粒)技术是指将原有的系统单芯片架构打散成多个独立的芯粒,而要把这些芯粒通过先进封装技术整合到一起之后,还需要能够高速互联起来,而怎么去实现各个芯粒之间高速互联,则是需要一个统一的互联标准。

此前,众多的芯片厂商都在推自己的互联标准,比如Marvell在推出模块化芯片架构时采用了Kandou总线接口;NVIDIA推出的用于GPU的高速互联NV Link方案;英特尔免费向外界授权的AIB高级接口总线协议;台积电也有TSMC和Arm合作搞了LIPINCON协议;AMD也有Infinity Fabrie总线互联技术,以及用于存储芯片堆叠互联的HBM接口等等。

但是,随着Chiplet技术的逐步发展,未来来自不同厂商的芯粒之间的互联需求,必然会爆发。特别是对于IP厂商来说,其商业模式可能会由卖IP转向“IP芯片化”,即半导体IP核以硅片的形式提供,IP就是“芯粒”,可以实现IP的“即插即用”和“重复利用”,以解决原有先进制程工艺芯片面临的性能与成本的矛盾,并降低较大规模芯片的设计时间和风险,实现从SoC中的IP到SiP封装中以独立的芯粒形式呈现的IP。但是,如果各家芯片厂商都在推自己的标准,这将导致不同厂商的Chiplet之间的互联障碍,限制Chiplet的发展。

在此背景之下,如果能够有一个统一的Chiplet互联标准,那么自然将加速整个Chiplet生态的发展。于是,作为头部的处理器大厂及晶圆代工厂,自然是有动力来共同形成一个统一的标准来解决这一问题。

UCIe详解

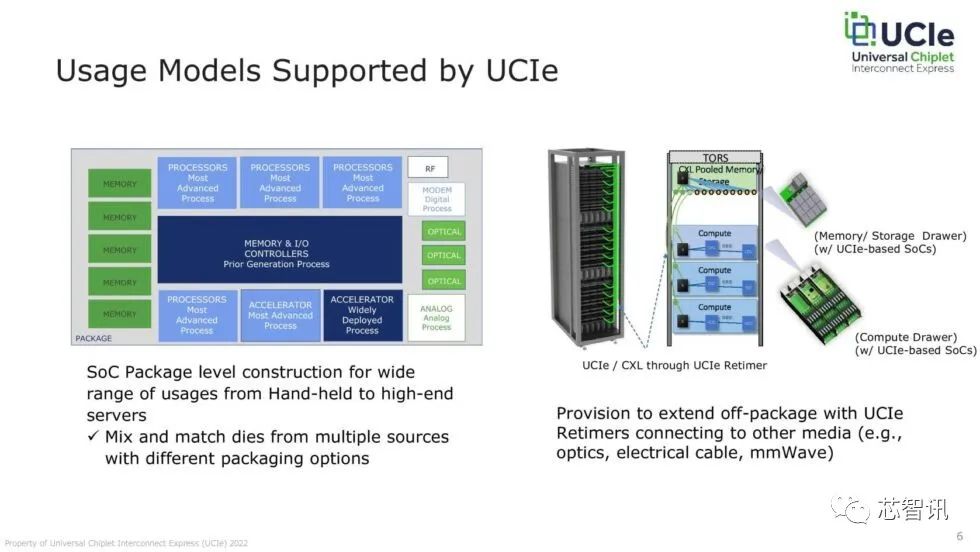

据介绍,UCIe 互连将实现Chiplet(如内核、内存和 I/O)之间的标准化连接,其外观和操作类似于片上连接,同时还支持与其他组件的片外连接。这些设计甚至可以实现足够低的用于机架级设计的延迟和足够高的带宽,并且依赖于现有协议,如 PCIe 和 CXL(Compute eXpress Link )。

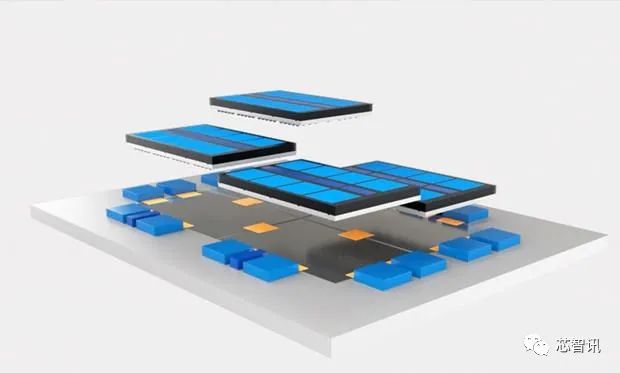

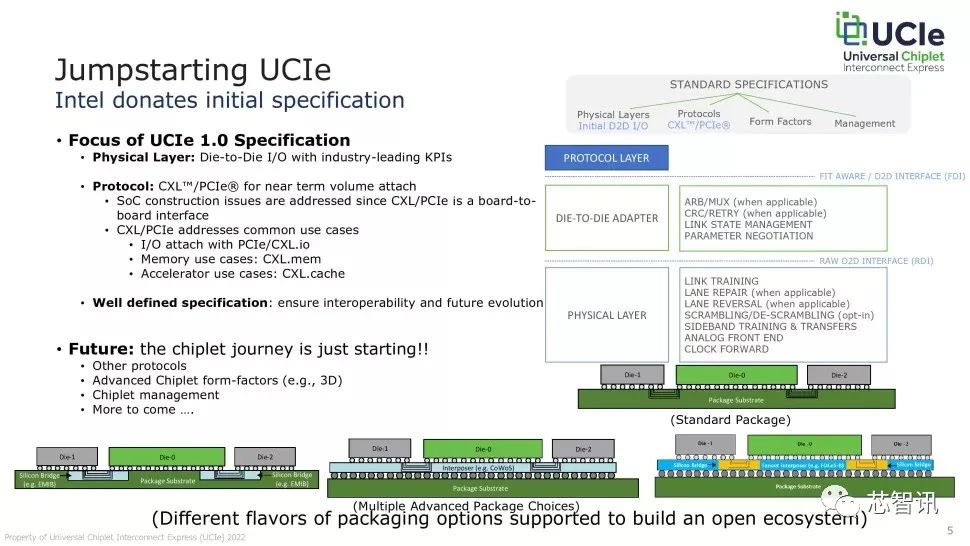

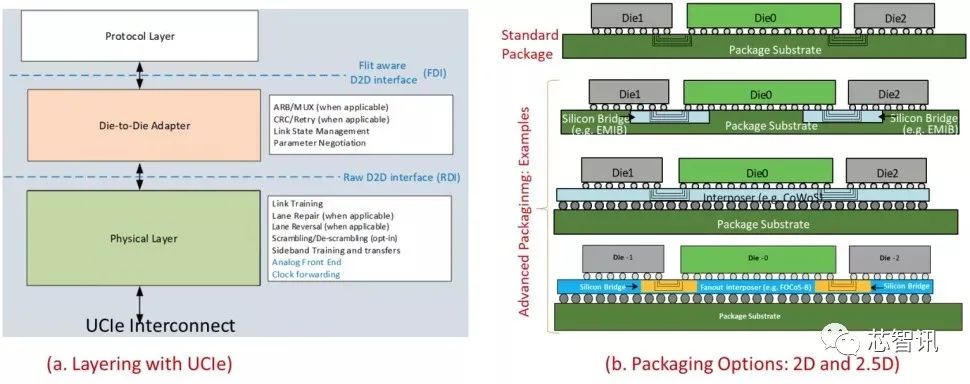

具体来说,UCIe 是一种分层协议,具有物理层和 die-to-die 适配器。物理层可以包含来自多家不同公司的所有类型的当前封装选项。这包括标准 2D 封装和更先进的 2.5D 封装,如英特尔的EMIB、台积电基于中介层的 CoWoS,以及扇出中介层方法,如 FOCoS-B。UCIe 标准未来也将最终扩展到 3D 封装互连。

UCIe的协议层运行在物理层之上,最初的规范依赖于 PCIe 或开放的CXL(最初由英特尔捐赠) 协议。PCIe 协议提供广泛的互操作性和灵活性,而 CXL 可用于更高级的低延迟/高吞吐量连接,如内存 (cxl.mem)、I/O (cxl.io) 以及 GPU 和 ASIC (cxl) 等加速器、缓存。虽然该规范以 PCIe 和 CXL 作为当前协议开始,但将来会扩展到包括其他协议。

英特尔之前曾为 EMIB 使用过两种协议:高级互连总线 (AIB) 和 UIB。英特尔捐赠 AIB 作为开源免版税之前试图建立标准化的小芯片生态系统的标准,但这并没有获得太多的厂商跟进。相比之下,CXL 现在是一种被广泛采用的标准,因此将它与 UCIe 一起使用更有意义。但是,UCIe 和 AIB 在本质上并不兼容(特殊的子集设计可以同时使用两者),因此尽管英特尔将继续完全支持当前的 AIB 实施,但它将停止所有进一步的开发并迁移到 UCIe。

此外,UCIe 规范还包括一个重定时器设计,可以扩展芯片封装外的连接,实现与其他组件的光学和电气连接,例如池化内存、计算和加速器资源。鉴于出色的性能指标,UCIe 联盟设想该互连标准最终将使该行业几十年来一直在努力构建有意义的数量的机架级分解系统类型成为可能。芯片到机架的连接可以使用原生 CXL 进行 PCIe 通信(无需转换),或许最终提供此类设计所需的低延迟和带宽。此外,如果需要,可以使用其他类型的协议。

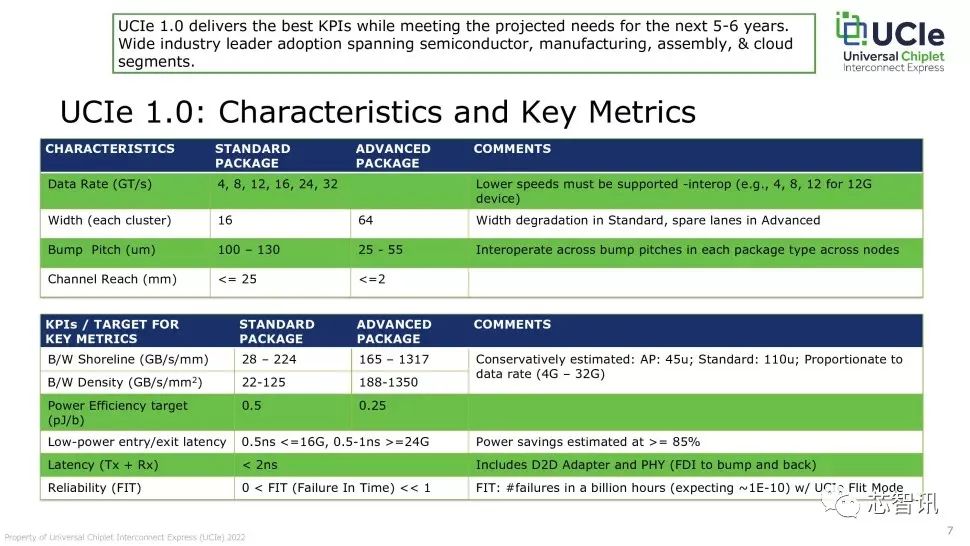

UCIe联盟还给出了非常激进的性能和面积目标,并且有许多活动部件可以为广泛的用途定制连接,不仅仅是最高端的设备。该联盟将目标划分为两个广泛的范围,使用标准的2D封装技术和更先进的 2.5D 技术(EMIB、CoWoS 等)。当然,先进的封装选项提供了更高的带宽和密度。

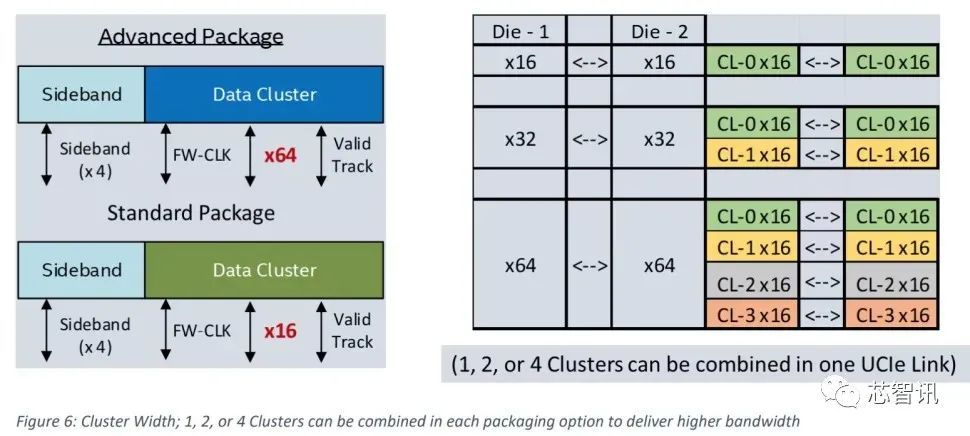

可配置因素包括数据的传输速率( 4 到 32 GT/s)、宽度(通道数)、凸块间距(连接密度)和通道范围(物理连接的长度,2毫米到25毫米)、延迟在 2 纳秒以下。

对于追求高性能的设计,通常都是将尽可能多的降低延迟和提升带宽,并占用更小的面积。然而,大多数设计不需要那种水平的性能,因此设计师可以利用多种选项来定制他们的设计。因此,“关键指标目标”部分将根据各种不同的设计选择而有所不同。

例如,带宽的Shoreline (GB/s per MM) 和 带宽密度 (GBs per mm^2) 预测基于 45 微米凸块间距。但是,该规范支持低至 25 微米的凸块间距,这将使这些值增加三倍或更多。这意味着对于 UCIe 连接,我们可以看到每平方毫米的吞吐量高达3.8 TB/s。但是,放宽这些值可以提高电源效率,突出显示可用于满足几乎任何用例的多个优化轴。此外,UCIe联盟在构建规范时考虑了电源效率,适应了诸如从开机和关机状态快速进入/退出(亚纳秒级)等高级功能。

总体而言,UCIe 规范旨在使得Chiplet封装互连尽可能类似于片上互连,同时提供大量选项,可以实现所需的任何类型的性能或封装技术。

虽然,Open Compute Project项目组推出的Bunch of Wires (BoW) 规范也同样着眼于统一Chiplet互联标准。BoW 规范旨在使Chiplet设计自主化,并拥有令人印象深刻的性能规范,但它并不那么灵活。例如,BoW 提供 0.7 至 0.5 pJ/bit(皮焦耳/比特)的功率效率。相比之下,UCIe可用的各种选项可实现 0.5 至 0.25 pJ/bit 的任何功率效率(这可能因使用的制程节点而异)。此外,BoW 规范支持固定的 16 GT/s,而 UCIe 是可配置的,最高可扩展到 32 GT/s。而且UCIe 在其他指标方面也处于领先地位,例如带宽密度(1280 Gbps 对比高达 3.8 Tb/s),并且还仅限于 MCP 封装,而 UCIe 可以支持大多数 2D 和 2.5D 封装选项。

编辑:芯智讯-浪客剑 资料来源:tomshardware.com、uciexpress.org

任奇伟出任展锐代理CEO!楚庆遭免职后将加盟创业公司,估值已达60亿元?

美国制裁之下,台积电/格芯/英特尔/AMD等半导体大厂已断供俄罗斯

2021Q4全球智能手机芯片市场:联发科第一,展锐第四,华为份额仅剩1%

2022年全球CIS市场规模将达219亿美元:豪威科技将拿下12.9%份额

三星晶圆代工疑“良率造假”,4nm良率仅35%?传高通3nm芯片将全面转向台积电

豪威科技推出全球最小0.56μm像素技术:将基于台积电28nm打造2亿像素CIS芯片

英特尔全系产品及技术路线图公布:Arrow Lake首发2nm工艺,2024年上半年量产

行业交流、合作请加微信:icsmart01

芯智讯官方交流群:221807116