非常实用的PCB布局布线规则,画出美而高性能的板子

一、布局

2. 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件.

3. 元器件的排列要便于调试和维修,亦即小元件周围不能放置大元件、需调试的元、器件周围要有足够的空间。

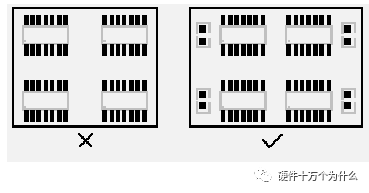

4. 相同结构电路部分,尽可能采用“对称式”标准布局;

5. 按照均匀分布、重心平衡、版面美观的标准优化布局;

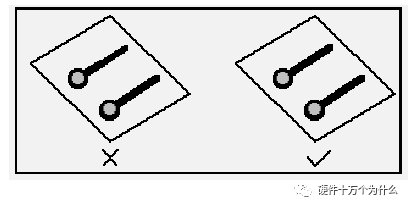

6. 同类型插装元器件在X或Y方向上应朝一个方向放置。同一种类型的有极性 分立元件也要力争在X或Y方向上保持一致,便于生产和检验。

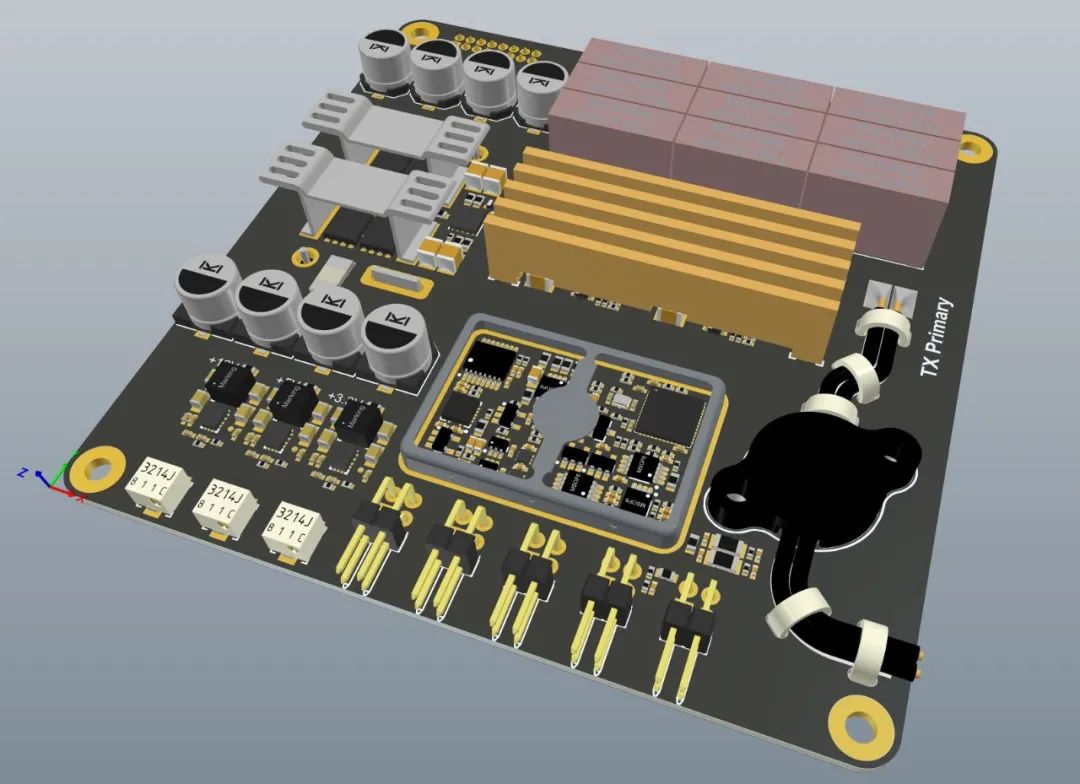

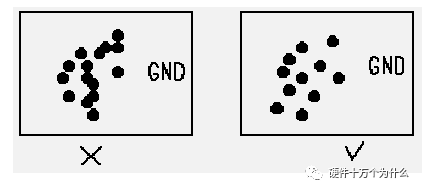

7. 发热元件要一般应均匀分布,以利于单板和整机的散热,除温度检测元件以外的温度敏感器件应远离发热量大的元器件。

8. 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分。

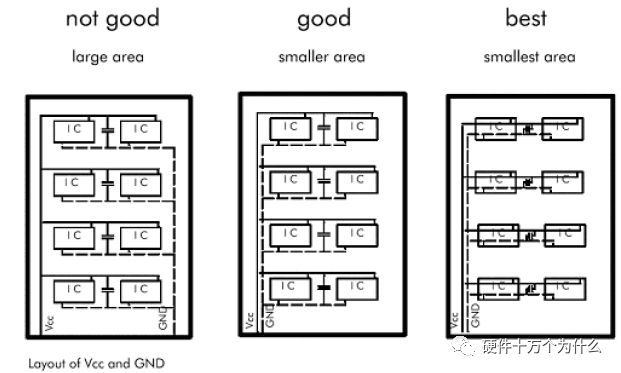

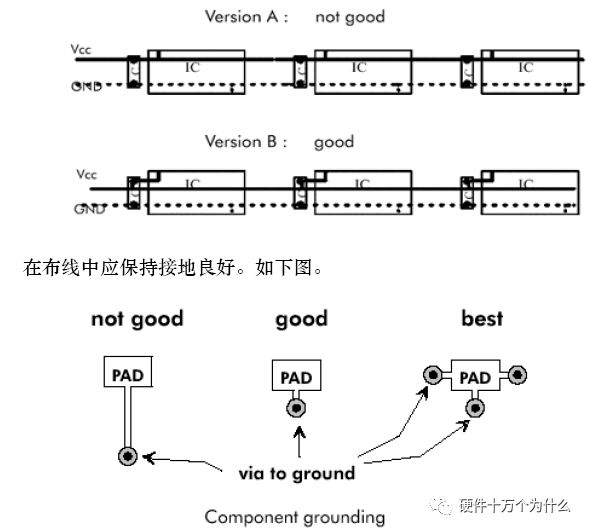

9、去耦电容的布局要尽量靠近IC的电源管脚,并使之与电源和地之间形成的回路最短。

10、元件布局时,应适当考虑使用同一种电源的器件尽量放在一起, 以便于将来的电源分隔。

二、布线

(1)布线优先次序

密度优先原则:从单板上连接关系最复杂的器件着手布线。从单板上连线 最密集的区域开始布线

注意点:

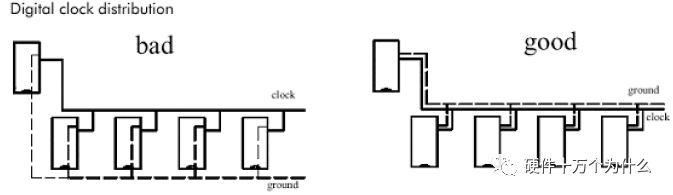

a、尽量为时钟信号、高频信号、敏感信号等关键信号提供专门的布线层,并保证其最小的回路面积。必要时应采取手工优先布线、屏蔽和加大安全间距等方法。保证信号质量。

b、电源层和地层之间的EMC环境较差,应避免布置对干扰敏感的信号。

c、有阻抗控制要求的网络应尽量按线长线宽要求布线。

(2)四种具体走线方式

1 、时钟的布线:

如果板上有专门的时钟发生芯片,其下方不可走线,应在其下方铺铜,必要时还可以对其专门割地。对于很多芯片都有参考的晶体振荡器,这些晶振下方也不应走线,要铺铜隔离。

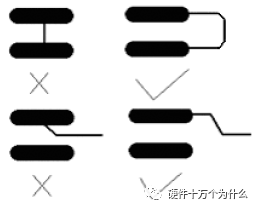

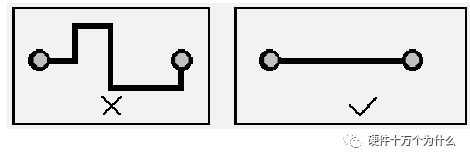

2、直角走线:

直角走线的对信号的影响就是主要体现在三个方面:

一是拐角可以等效为传输线上的容性负载,减缓上升时间;

二是阻抗不连续会造成信号的反射;

三是直角尖端产生的EMI。

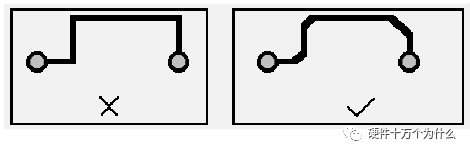

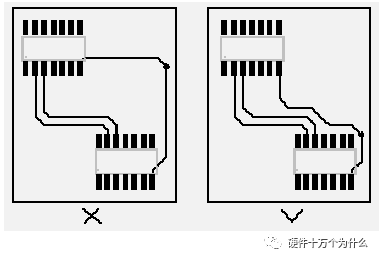

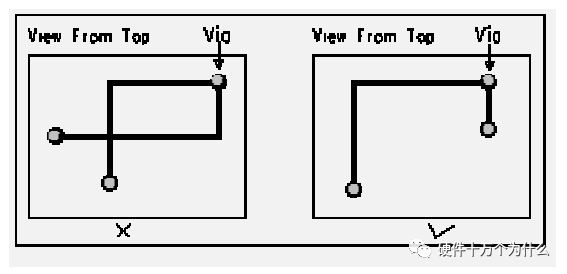

3、差分走线:

a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

等长是为了保证两个差分信号时刻保持相反极性,减少共模分量;等距则主要是为了保证两者差分阻抗一致,减少反射。“尽量靠近原则”有时候也是差分走线的要求之一。

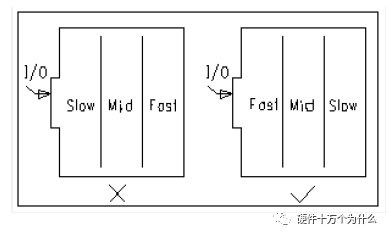

4、蛇形线:

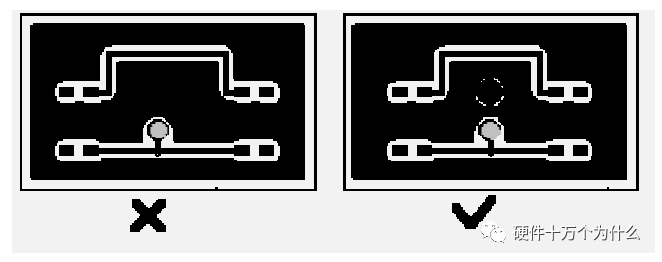

成对出现的差分信号线,一般平行走线,尽量少打过孔,必须打孔时,应两线一同打孔,以做到阻抗匹配。

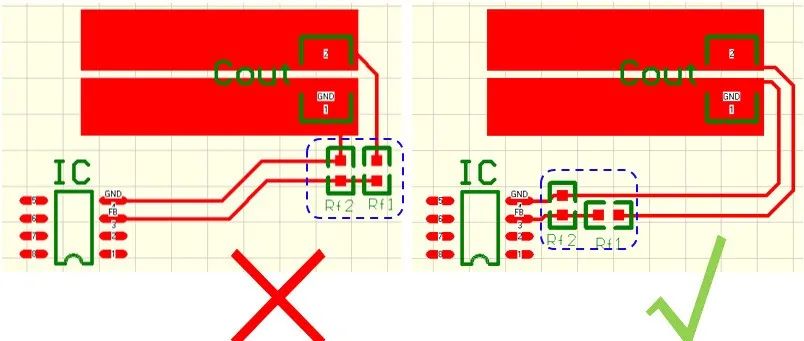

相同属性的一组总线,应尽量并排走线,做到尽量等长。从贴片焊盘引出的过孔尽量离焊盘远些。

1、走线的方向控制规则:

2、走线的开环检查规则:

4、走线长度控制规则:

5、倒角规则:

B. 在双层板设计中,一般应该使电流先经过滤波电容滤波再供器件使用。

C. 在高速电路设计中,能否正确地使用去耦电容,关系到整个板的稳定性。

7、器件布局分区/分层规则:

B. 对混合电路,也有将模拟与数字电路分别布置在印制板的两面,分别使用不同的层布线,中间用地层隔离的方式。

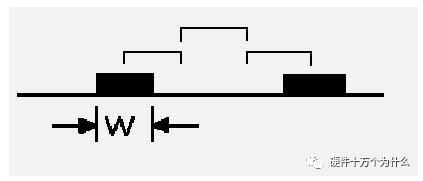

10、3W规则:

11、屏蔽保护

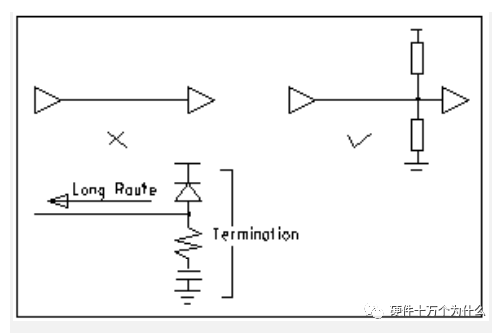

12、走线终结网络规则:

B. 对于点对多点(一个输出对应多个输出) 连接, 当网络的拓朴结构为菊花链时,应选择终端并联匹配。当网络为星型结构时,可以参考点对点结构。星形和菊花链为两种基本的拓扑结构, 其他结构可看成基本结构的变形, 可采取一些灵活措施进行匹配。在实际操作中要兼顾成本、 功耗和性能等因素, 一般不追求完全匹配,只要将失配引起的反射等干扰限制在可接受的范围即可。

13、走线闭环检查规则:

15、走线的谐振规则:

16、孤立铜区控制规则:

17、重叠电源与地线层规则:

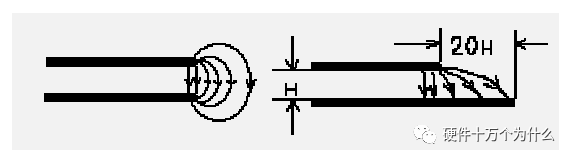

18、20H规则:

解决的办法是将电源层内缩, 使得电场只在接地层的范围内传导。以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

(4)其他

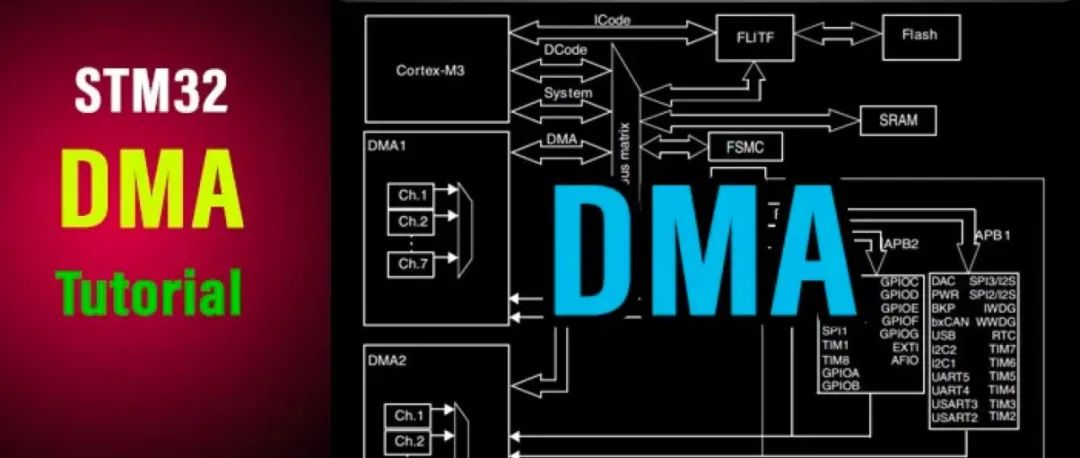

干货 | 一文讲透STM32串口DMA收发机制

这些“黑话”只有PCB设计制造内行人才懂!附PCB术语及英文对照

真实案例分享:MOS管电源开关电路,遇到上电冲击电流超标

干货分享:PCB Layout的设计要点

评论