最硬核毕业证:带着自己设计的芯片毕业,国科大16级本科生交付「一生一芯」首期成果

热文导读| 点击标题阅读

来自:知乎,作者:包云岗 链接:https://www.zhihu.com/question/409298856/answer/1363569013

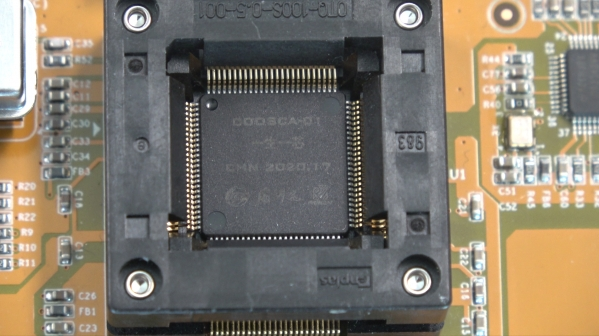

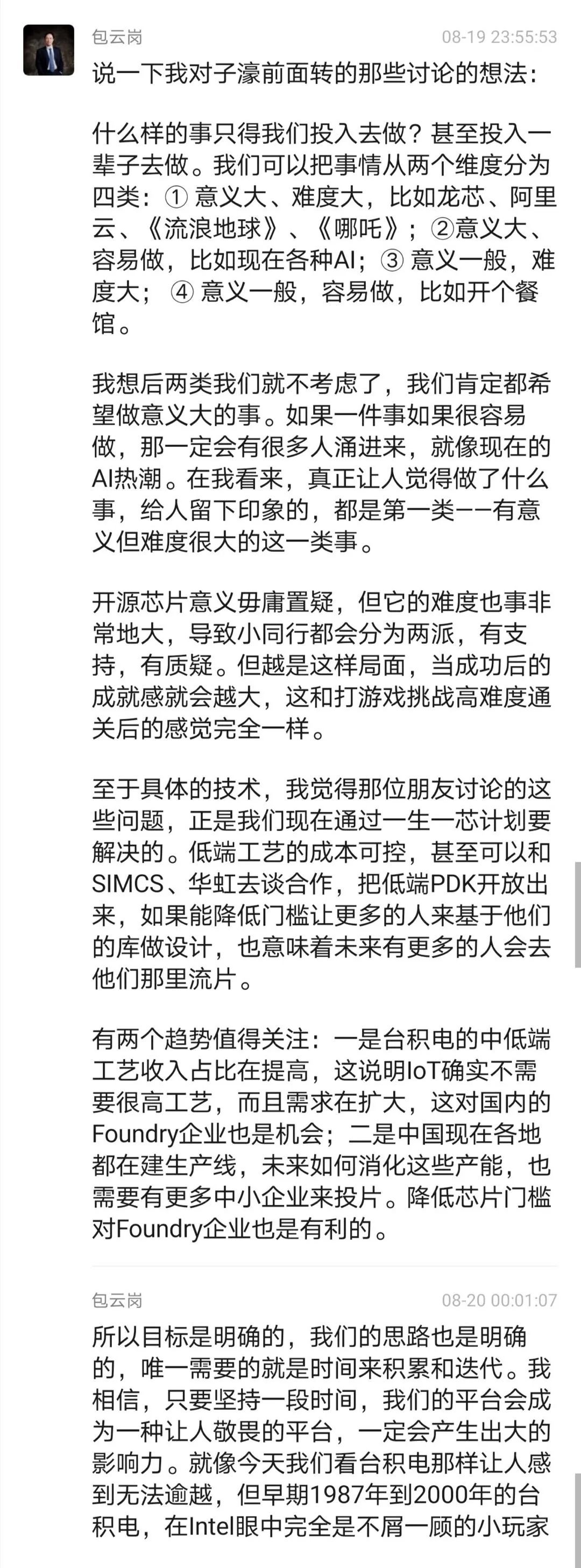

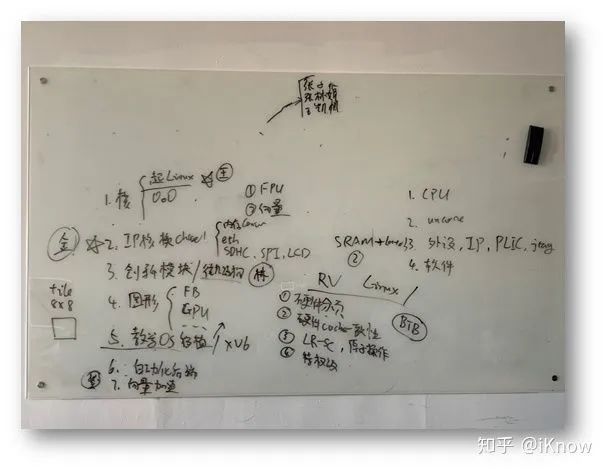

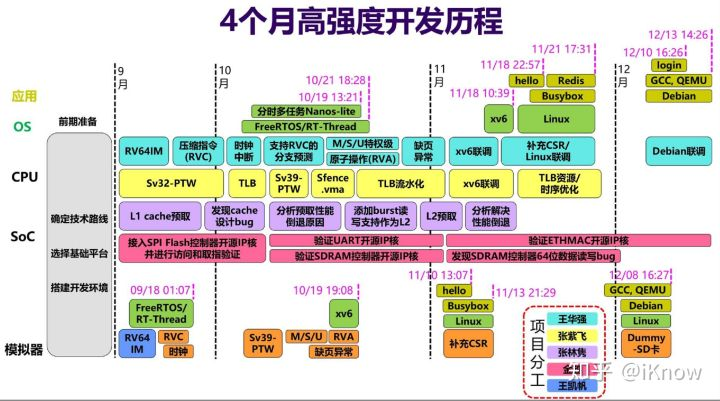

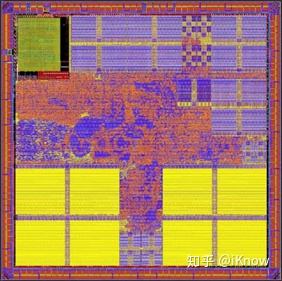

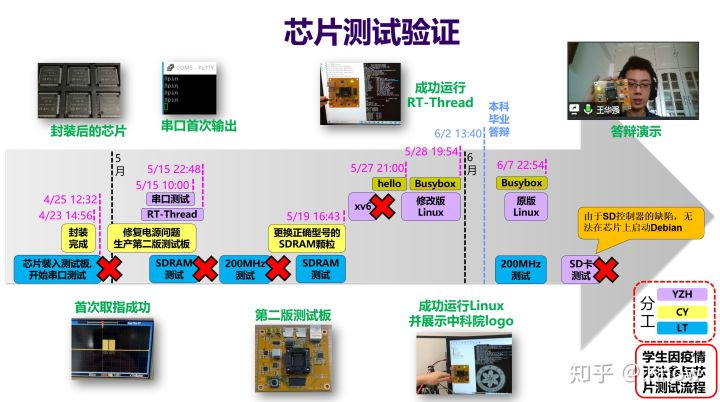

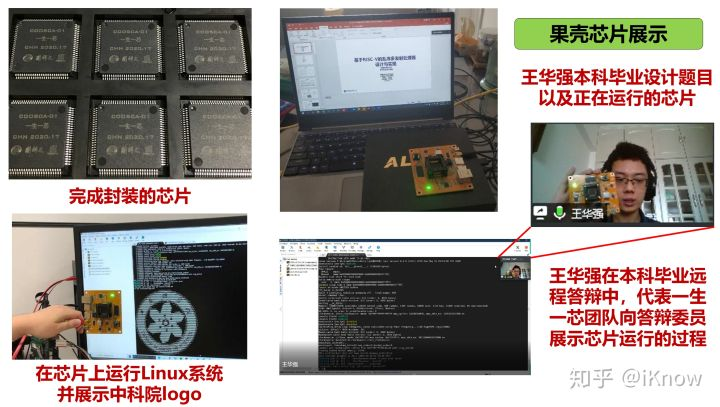

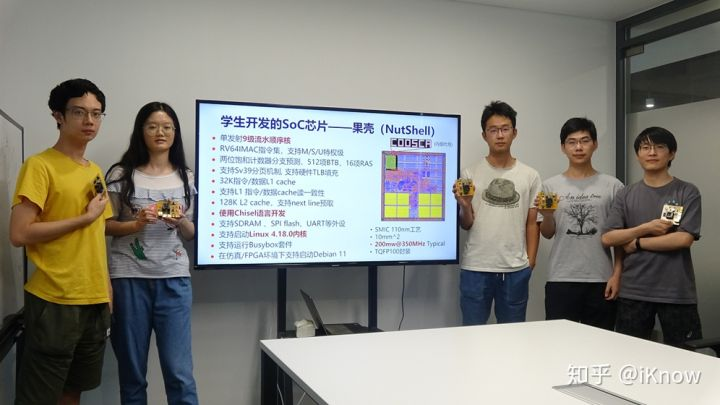

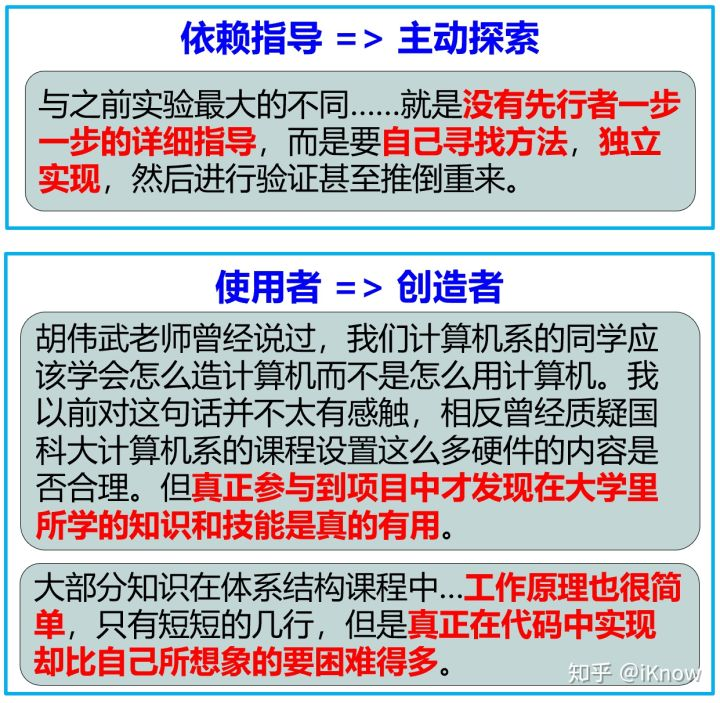

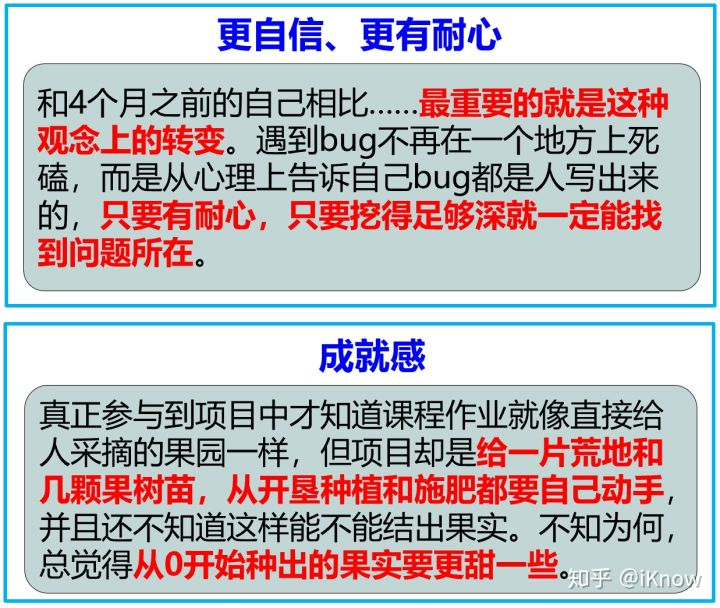

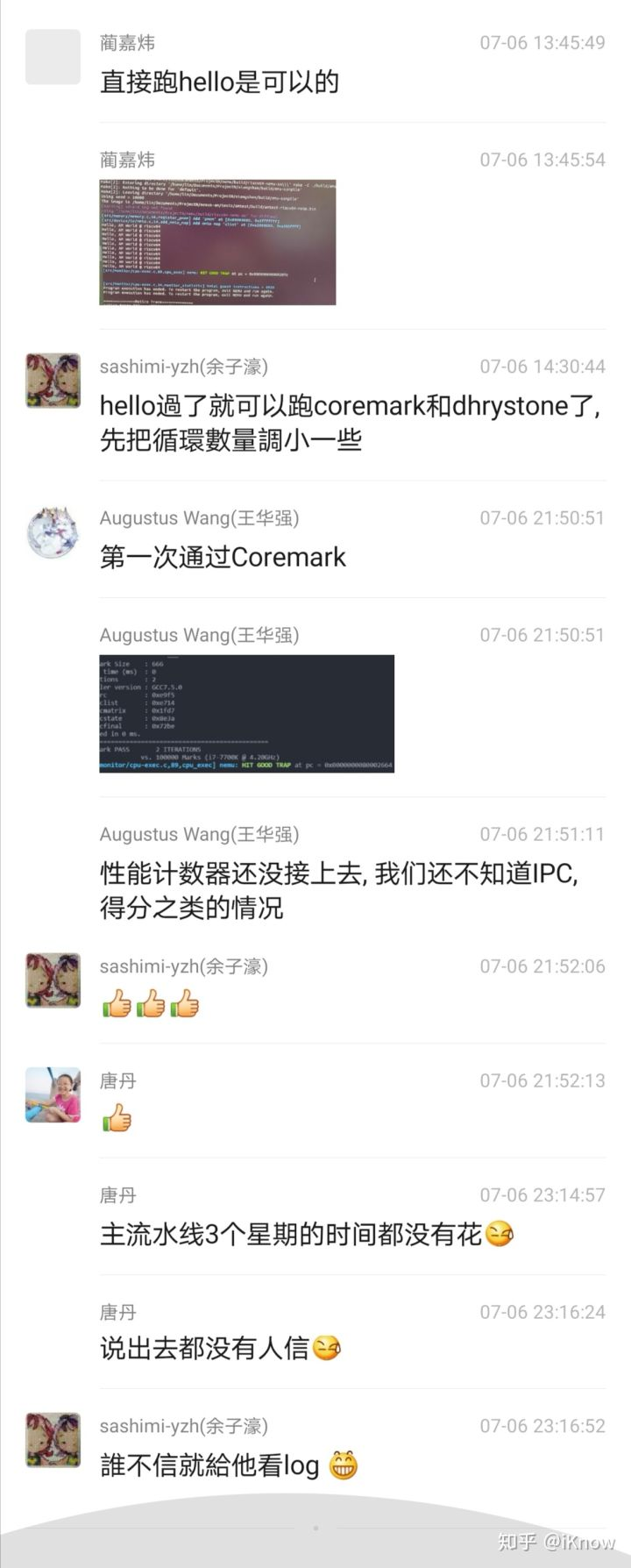

近日,五位来自中国科学院大学的 2016 级本科生,带着自己设计的处理器芯片「果壳」正式毕业,这一成果引发媒体热议,被网友称为「最硬核毕业证」。作为「一生一芯」计划的负责人,中科院计算所研究员包云岗也在社交平台上阐述了本次探索与实践背后的故事。

包云岗:「一生一芯」背后的故事

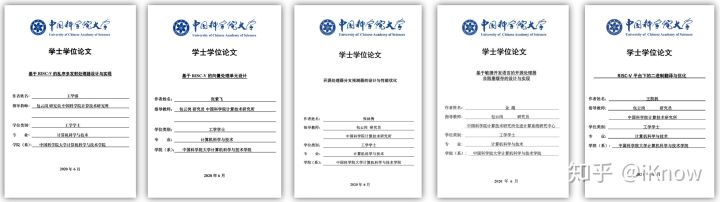

王华强:《基于 RISC-V 的乱序多发射处理器设计》

张紫飞:《基于 RISC-V 的向量处理单元设计》

张林隽:《开源处理器分支预测器的设计与性能优化》

金越:《基于敏捷开发语言的开源处理器非阻塞缓存的设计与实现》

王凯帆:《RISC-V 平台下的二进制翻译与优化》

为国科大发布会准备的视频,最后有彩蛋

最后,再看一下「一生一芯」计划的宣传视频吧:

开发者全社区

5T技术资源大放送!包括但不限于:Android,Python,Java,大数据,人工智能,AI等等。关注公众号后回复「2T」,即可免费获取!!

我们的知识星球第三期开期了,已达到1100人了,能连续做三期已很不容易了,有很多老用户续期,目前续期率达到50%,说明了大家对我们的知识星球还是很认可的,欢迎大家加入尽早我们的知识星球,更多星球信息参见:

说两件事

微信扫描或者点击上方二维码领取的Android \ Python的\ AI \的Java等高级进阶资源

更多学习资料点击下面的“阅读原文 ”获取

谢谢老板,点个好看↓

评论