RAMP Gold众核微处理器加速平台

众核微处理器加速平台 RAMP Gold

传统单核研究开发方法具有硬件服型开发周期长、软件模拟器慢、软硬件不能同时开发等缺点,这些缺点在面临规模急剧膨胀的多核研究时更加凸显,几乎无法用于解决多核处理器的研究问题。并行可能是过去 50 年中面对计算时的遇到的最大挑战,前人曾大量尝试解决通用并行计算问题,但一直没有令人满意的方法。多核处理器系统的研究开发使得业界迫切需要创新的解决方法,相比单核研究,这需要更加广泛的软硬件协同开发。

正是在这一背景下,源自著名国际会议 ISCA2005 上的一次讨论,众核微处理器加速平台( Research Accelerator for Multiple Processors,RAMP)的思想产生了 RAMP,旨在创建一个低成本、可重构、高度并行的平台来加快多核处理器研究中的软硬件开发速度,并吸引各个领域( 体系结构、编译、操作系统和应用程序等)的研究者来一起致力于解决并行计算的挑战。RAMP 的工作主要是开发和共享用于研究并行体系结构所需的软硬件基础:平台/工具,具有低成本、低功耗、快速、灵活、可观测、可再现及可信性等诸多特性。RAMP 平台采用多 FPGA 模拟的方案,用 FPGA 以硬件的速度级来模拟高度并行体系结构。

在学术界,伯克利、奥斯汀、麻省理工、斯坦福等着名大学均参与了 RAMP 项目;在业界,微软、IBM 、Xlinx、Intel 等国际大公司也参与合作,并提供技术支持 RAMP 的出现给并行及多核研究的带来了新途径。经过 5 年的发展, RAMP 经历了成长发展,产生了日益广泛的影响,日趋成熟本文在分析 RAMP 相关的重要论文和报告资料等基础上,从体系结构、研究课题、发展趋势等方向对 RAMP 进行简介、归纳和分析评价。

RAMP Gold

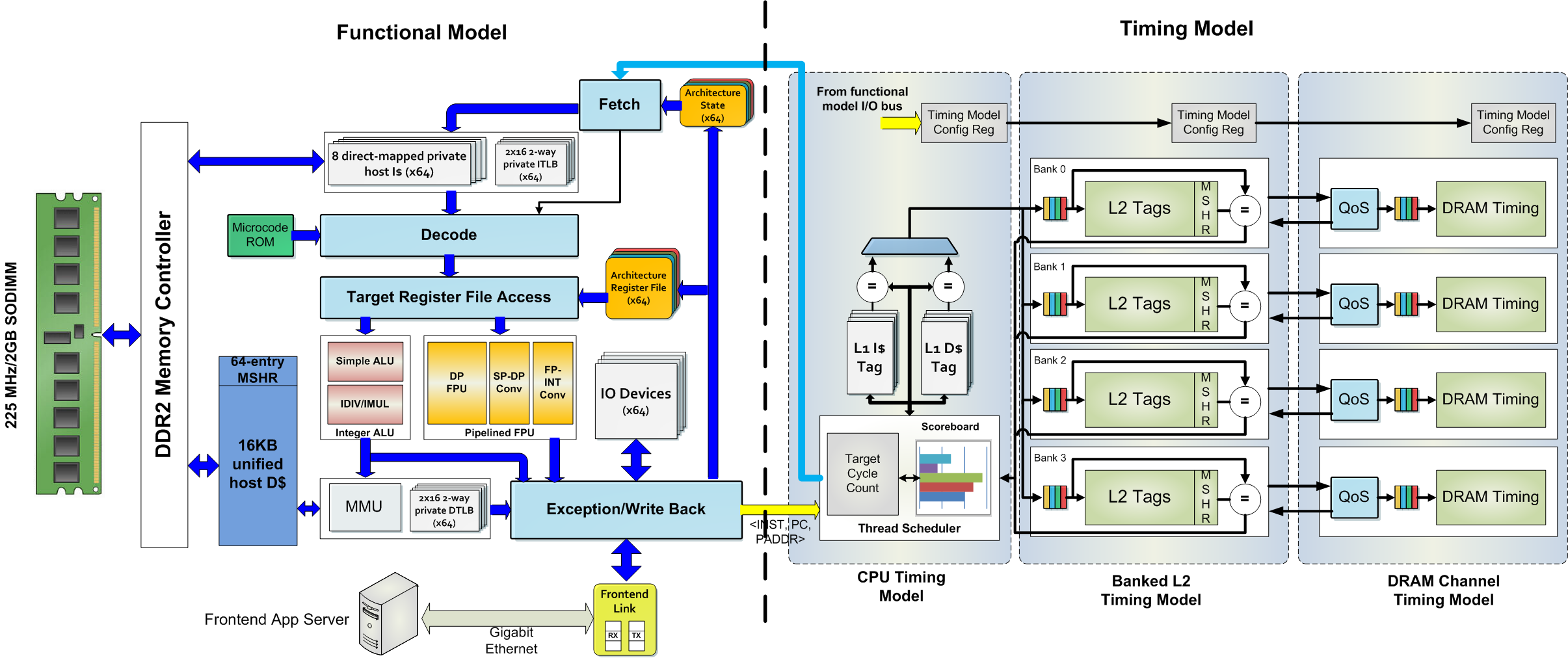

开发众核处理器参考模型采用高度多线程的分离的时序和功能模型,用于众核体系结构实验,操作系统、编程语言和实时并行应用的开发。

RAMP Gold 包括大约 36,000 行 SystemVerilog 和最小的第三方 IP 块。我们的第一个生产系统针对 Xilinx Virtex-5,并部署在一个低成本的 XUP 板上。

RAMP Gold 采用了许多先进的 FPGA 优化,并从头开始设计,并考虑到可靠性。下图显示了 RAMP Gold 的结构。时序和功能模型都是主机 - 多线程。功能模型维护架构状态并正确执行 ISA。时序模型确定指令在目标机器中执行所花费的时间以及调度线程以相应地在功能模型上执行。功能和时序模型之间的接口被设计为简单和可扩展的,以便于快速评估替代目标存储器层次结构和微架构。