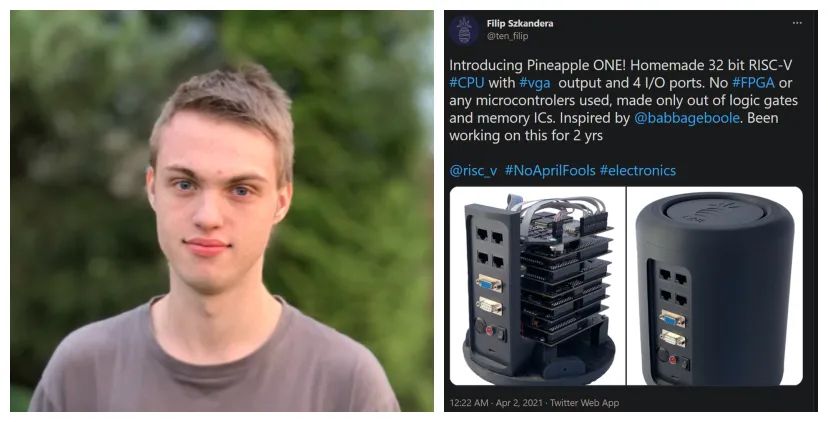

强!自制CPU,这个小伙办到了

RISC-V CPU,并构建了与其他自制计算机不同的个人计算机「菠萝一号(Pineapple ONE)」。从设计、调试和安装 CPU 和所有硬件,Filip 整整花了两年时间。

Filip 还受邀在东京举办的 RISC-V Days Tokyo 2021 Spring 上做了演示,他也成为了该会议自 2017 年举办以来最年轻的演示者。

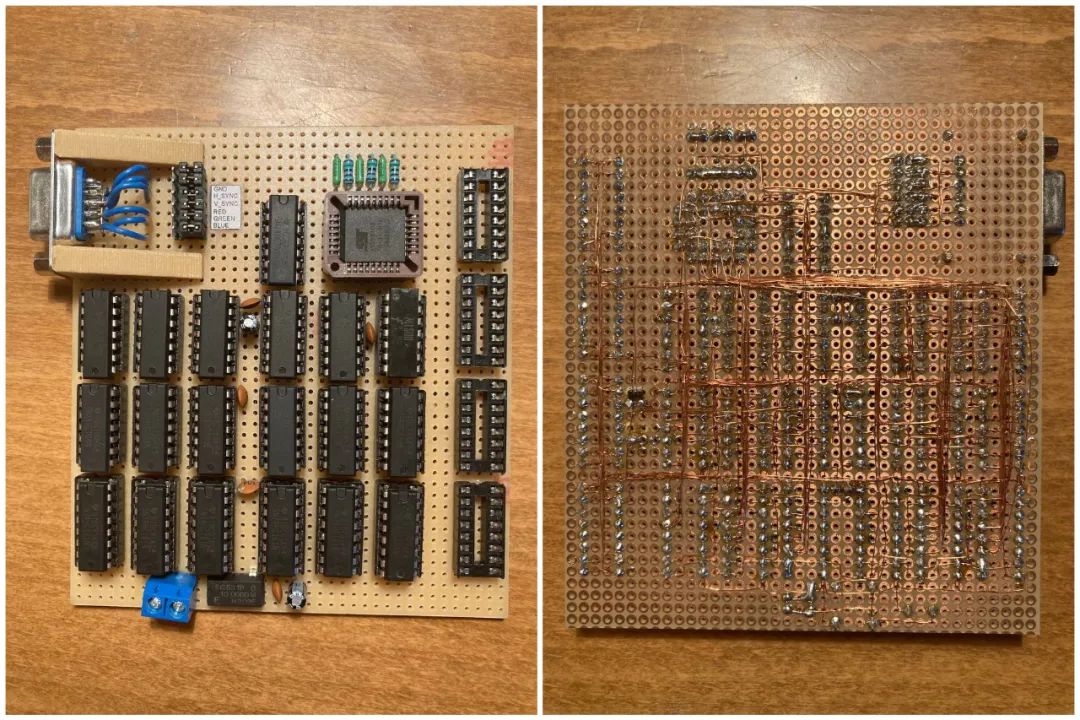

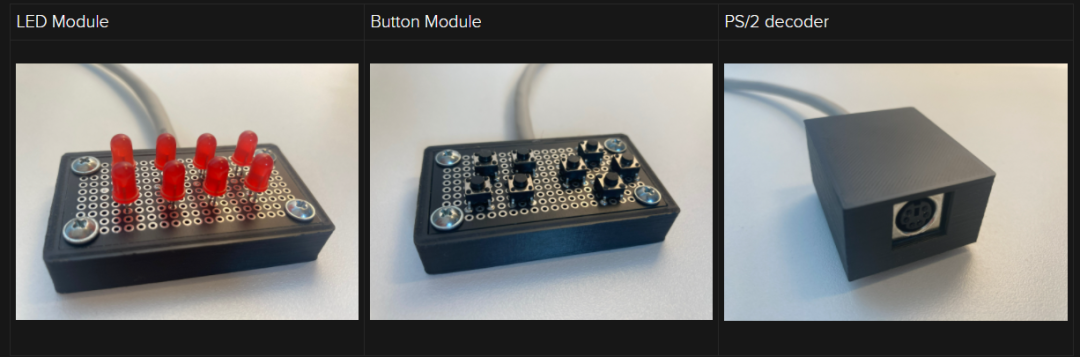

整体来看,「菠萝一号」是由 8 块正方形打印电路板垂直堆叠组成,每块边侧高度约为 10 厘米,外加一个 VGA 显示接口卡。

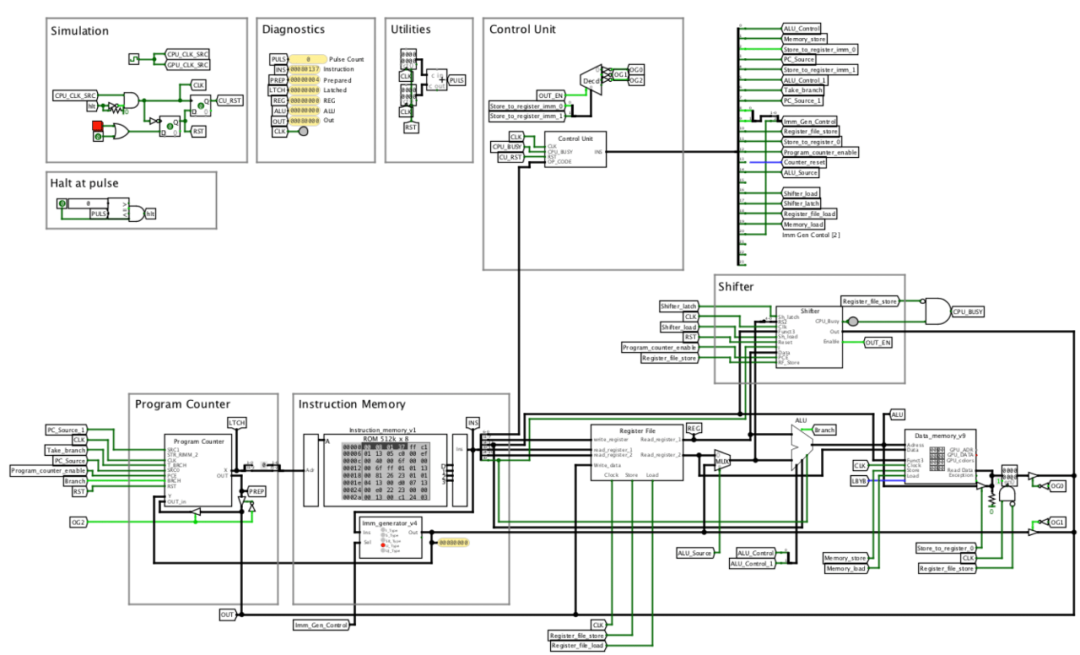

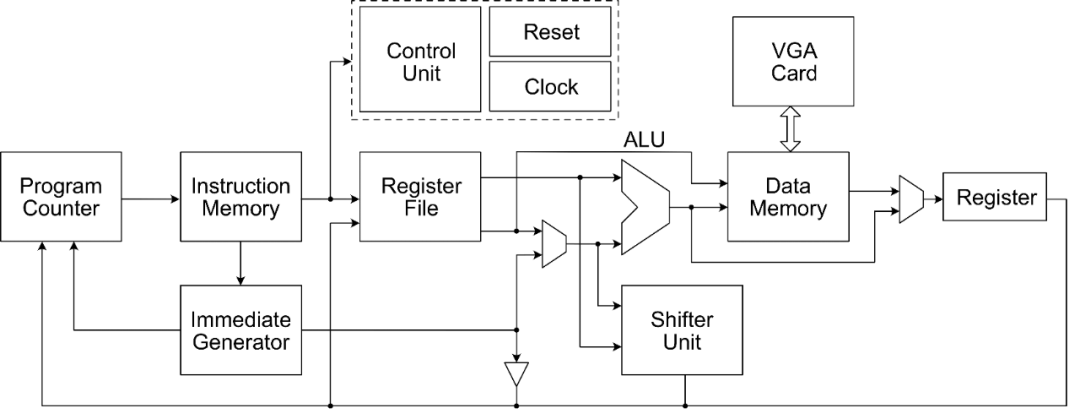

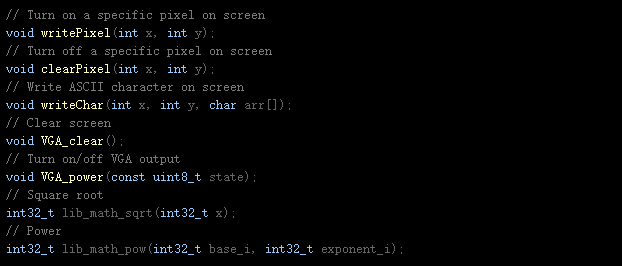

一共使用了 230 多个集成电路,大多数是 74HCT 系列逻辑芯片。示意图如下:

32 位 RISC-V CPU 的规格如下:

最大时钟速度:500kHz 程序内存:512kB 内存 512kB 闪存 512kB VGA 输出:200×150px(黑白) 2 个 8 位输入端口 2 个 8 位输出端口

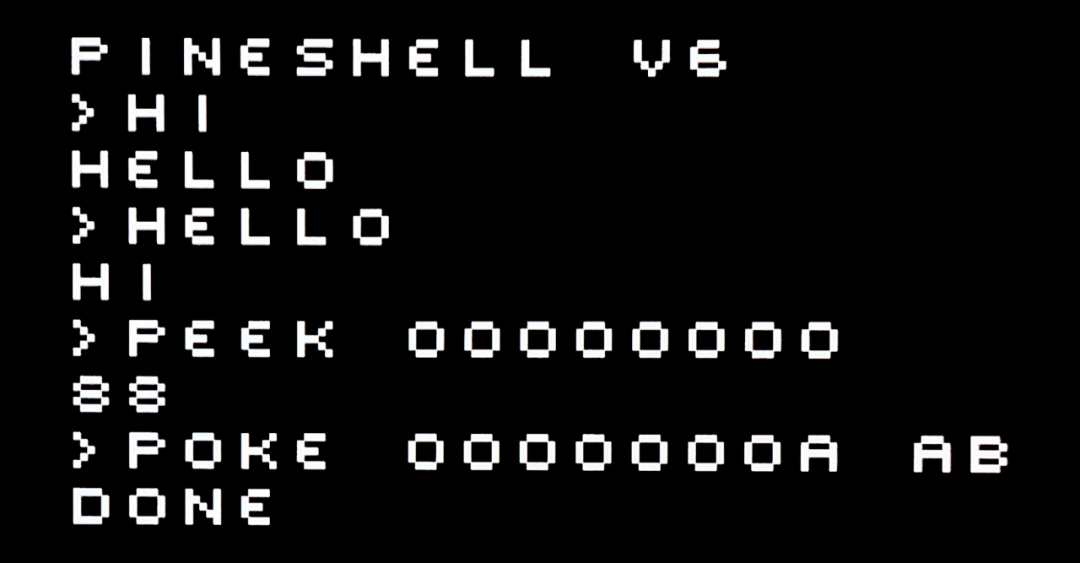

目前,「菠萝一号」计算机支持的命令包括:HELLO、HI、PEEK <ADDRESS>、POKE <ADDRESS> <DATA>、SYSTEM INFORMATION、CLEAR 等。

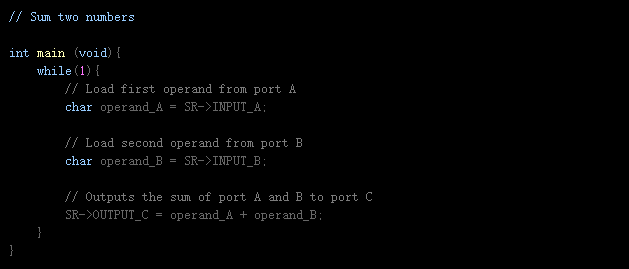

此前,我在 Youtube 上发现了电子爱好者 Ben Eater 自制 CPU(构建著名的 8 位计算机和经典的 6502 微处理器)的相关教程,所以非常着迷,也就有了自制 CPU 的想法。

然而,我觉得对于 CPU 基础知识了解的还不够,因此又观看了 Google Robotics 软件工程师 Robert Baruch 的教程视频,他只使用了基本逻辑元件构建了 32 位 RISC-V CPU。

之后,我便开始在一个名为「Logisim-Evolution」的项目中制造自己的 RISC-V CPU。

我给自己设定的目标是不使用任何微控制器或 FPGA,只使用基本的分立逻辑元件。

编译器支持的最基础 RISC-V CPU 必须包含扩展「整数(I)」且至少为 32 位。

此外,我还需要安装一个 VGA(视频图形阵列)输出卡。

我花了整整 6 个月的时间在 Logisim 项目上,终于得到一个可运行的程序模拟。

下一步绘制所有模块的原理图、从 JLCPCB 网站上购买所有的 PCB(印制电路板)并重新设计。

由于这是我首次购买 PCB,担心搞砸一切,于是决定在设计过程中分模块处理,一次选购几个,以免自己应接不暇。

Logisim-Evolution 项目中的模拟原理图如下:

经过了两轮设计,最后只剩下几个模块需要处理,其中一个是直接生成器(immediate generator)。

当我绞尽脑汁想将它从模拟转化为合适的原理图时,发现自己犯了一个致命错误:完全不清楚模拟是如何运行的。

幸运的是,修复起来也没有那么困难,于是对已经制作完成的 PCB 做了改进。

接下来,我将开源电子原型平台 Arduino 连接到每个 PCB 的输入端、同时监控输出端并与预测端(prediction)做对比,从而对这些 PCB 进行测试。设置好之后,一切就可以自动运行了。

每次测试都至少持续数个小时。

当我准备好将所有 PCB 整合到一块时,模块也已经间隔地安装在了木头上,并使用 3D 打印垫片(spacer)来固定。接着上传了一个测试程序并开始测试。

原型机示意图如下:

大功告成!

推荐阅读

• 硬核图解,再填猛将!• Python实现的导弹跟踪算法,燃!• 看书vs视频,我的一点小建议,共勉!