一款革命性的Arm处理器

导读:大约50年前,英特尔创造了世界上第一个商业生产的微处理器,一个普通的4位CPU(中央处理器),2300个晶体管,使用10μm工艺技术在硅中制造,只能进行简单的算术计算。自这项突破性的成就以来,技术不断发展,越来越复杂,目前最先进的64位硅微处理器已经拥有300亿个晶体管(例如,AWS Graviton2微处理器,使用7纳米工艺技术制造)。

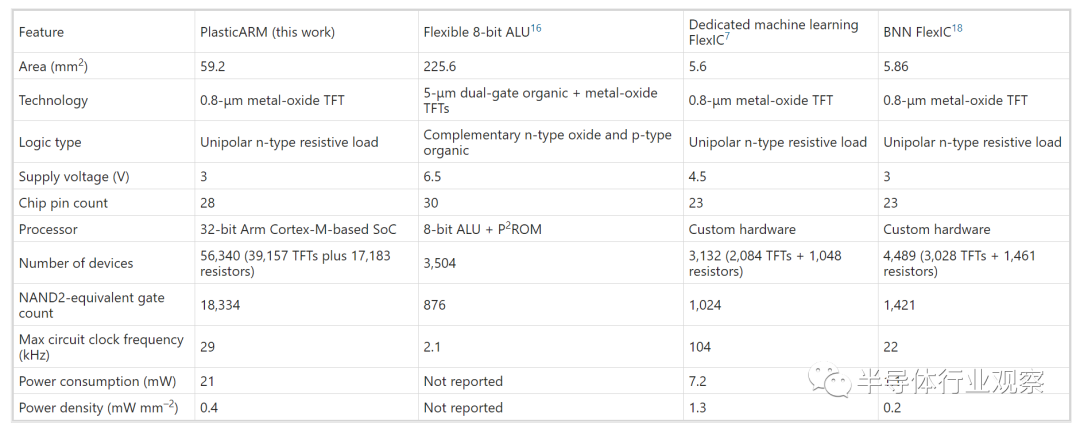

本文报道了一种32位Arm架构的微处理器,采用金属氧化物薄膜晶体管技术在柔性衬底(PlasticARM)上开发。与主流半导体行业不同,柔性电子产品通过超薄的外形、整合性、极低的成本和大规模生产的潜力,与日常用品无缝集成。PlasticARM是将数十亿个低成本超薄微处理器嵌入日常用品的先驱。

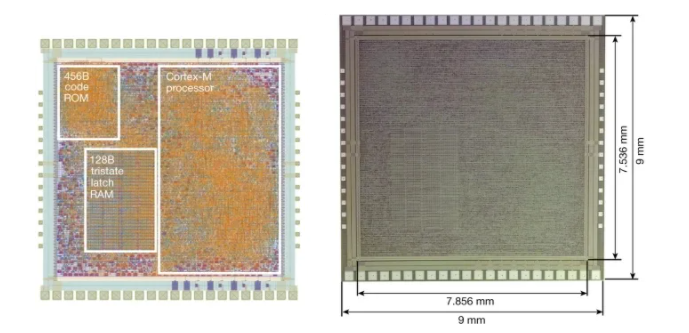

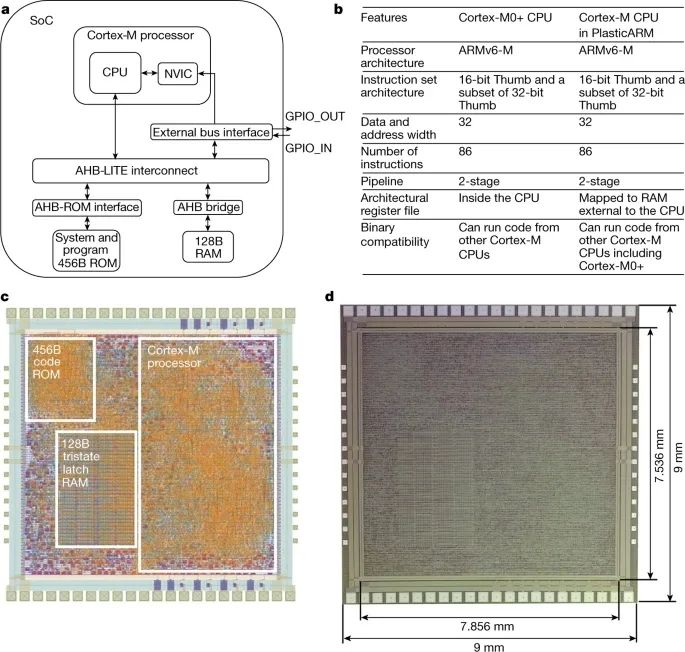

PlasticARM系统架构

结果

结论

方法

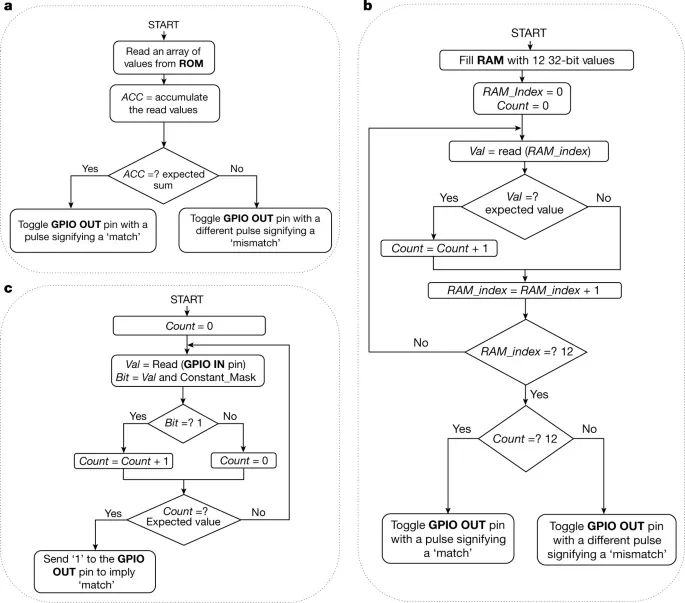

执行

制造

模拟、测试和验证

英文链接:

https://www.nature.com/articles/s41586-021-03625-w

1、行业深度报告:GPU研究框架

2、信创产业研究框架

3、ARM行业研究框架

4、CPU研究框架

5、国产CPU研究框架

6、行业深度报告:GPU研究框架

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕,知识点深度讲解,提供182页完整版下载。

获取方式:点击“阅读原文”即可查看PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。

评论