教你精确计算 I2C 上拉电阻阻值

I2C 总线能挂多少设备?

理论上:

7-bit address :2 的 7 次方,能挂 128 个设备。

10-bit address :2 的 10 次方,能挂 1024 个设备。

当然,要把预留设备地址去除,7 bit 协议规定了 8个预留地址,普通厂商不可以使用。保留地址如下:

但是 I2C 协议规定,总线上的电容不可以超过 400pF。管脚都是有输入电容的,PCB 上也会有寄生电容,所以会有一个限制。实际设计中经验值大概是不超过 8 个器件。

总线之所以规定电容大小是因为,I2C 使用的 GPIO 为开漏结构,开漏结构无法输出高电平,要求外部有上拉电阻拉高。电阻和总线电容产生了一个 RC 延时效应,电容越大信号的边沿就越缓,有可能带来信号质量风险。

传输速度越快,信号的窗口就越小,上升沿下降沿时间要求更短更陡峭,所以 RC 乘积必须更小。

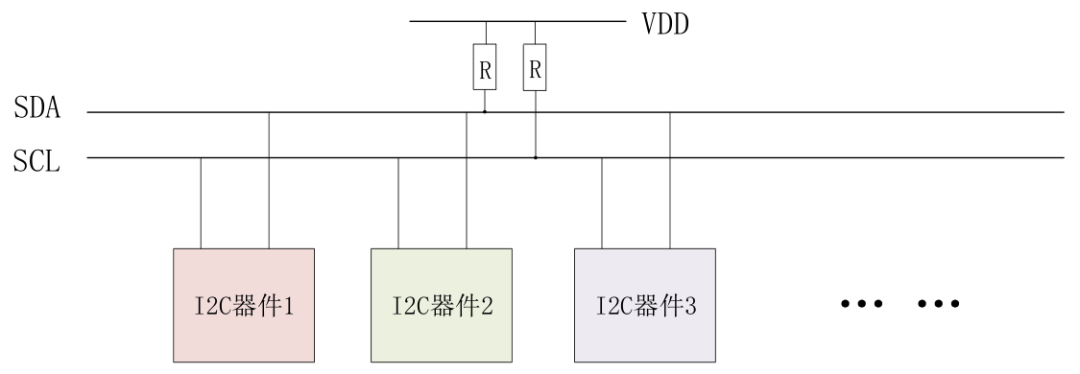

I2C 架构

我们知道 I2C 有不同的速度模式,标准(100KHz)、快速(400KHz)、快速plus(1MHz)、高速(3.4MHz)。

Vdd 可以采用 5V、3.3V、1.8V 等,电源电压不同,上拉电阻阻值也不同。

一般总线上认为,低于 0.3Vdd 为低电平,高于 0.7Vdd 为高电平。

上拉电阻计算

1、上拉电阻过小,总线上电流增大,端口输出低电平增大。

2、上拉电阻过大,上升沿时间增大,方波可能会变成三角波。

因此计算出一个精确的上拉电阻阻值是非常重要的。

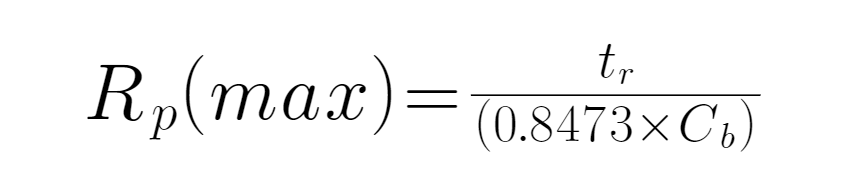

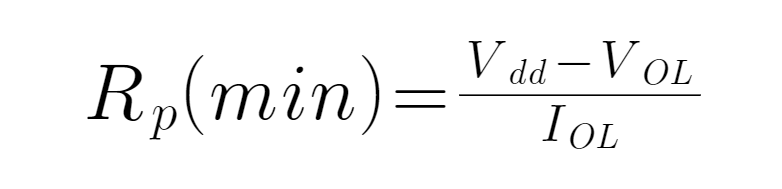

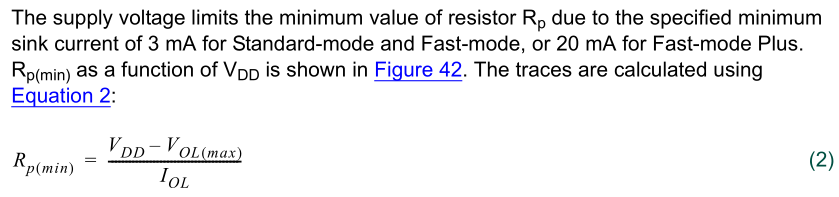

计算上拉电阻的阻值,是有明确计算公式的:

最大电阻和上升沿时间 tr 、总线电容 Cb 、标准上升沿时间 0.8473 有关。

最小电阻和电源 Vdd 电压、GPIO 口自己最大输出电压 Vol、 GPIO口自己最大电流 Vol 有关。

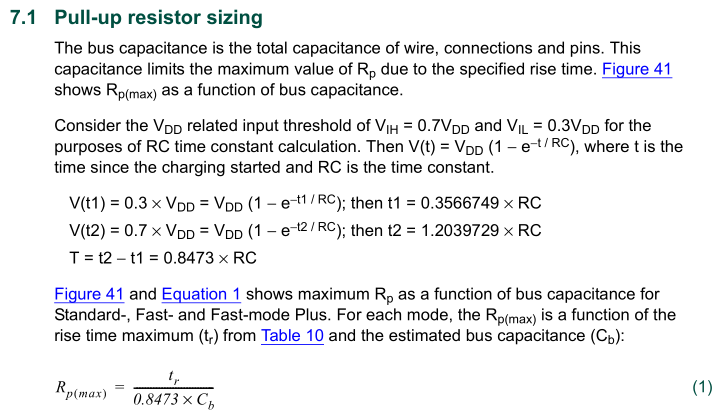

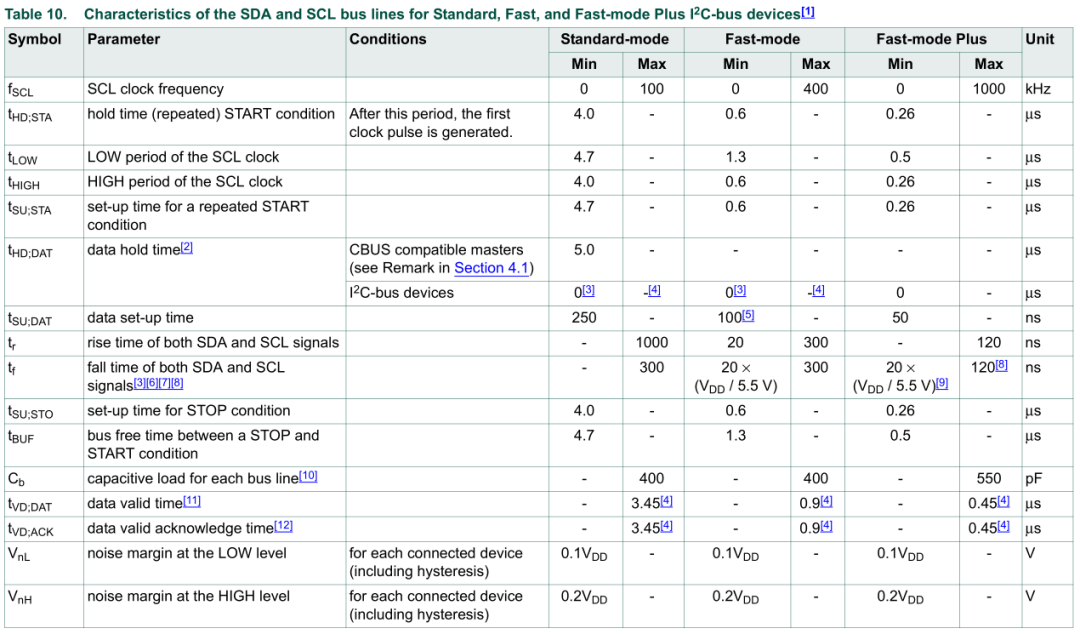

查《I2C-bus specification and user manual.pdf》7.1节:

查《I2C-bus specification and user manual.pdf》表10:

由上表可知:

1、标准模式:0~100KHz,上升沿时间 tr = 1us

2、快速模式:100~400KHz,上升沿时间 tr = 0.3us

3、高速模式:up to 3.4MHz,上升沿时间 tr = 0.12us

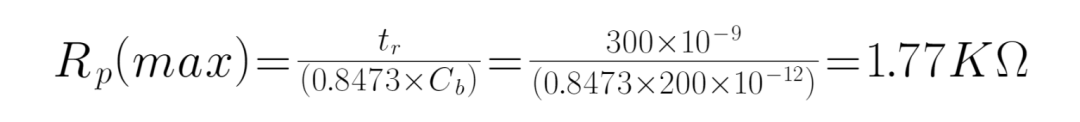

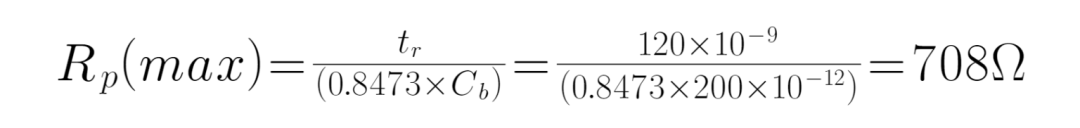

由此公式,假设 Vdd 是 1.8V 供电,Cb 总线电容是200pF(虽然协议规定负载电容最大 400pF,实际上超过 200pF 波形就很不好,我们以 200pF 来计算)

标准模式 :

快速模式:

高速模式:

最小电阻(Vdd越大,上拉电阻就要越大):

note:高速模式下,电源电压一般采用 1.8 V,不会采用 3.3V,因为如果用 3.3V 计算你会发现最小电阻比最大电阻大。

大家在不同速率采用的电阻一般有以下几种:1.5K、2.2K、4.7K。

一般大家采用 I2C 使用标准模式即可 ,也就是 100KHz,推荐上拉电阻是 4.7K,当然大家可以用示波器看传输波形,适当调整。

结论:I2C 上拉电阻阻值和电源电压、传输速度、总线电容(负载因素)都有关系,大家根据自己的板子计算一下即可,选取最优电阻阻值,从而获得最优传输波形。

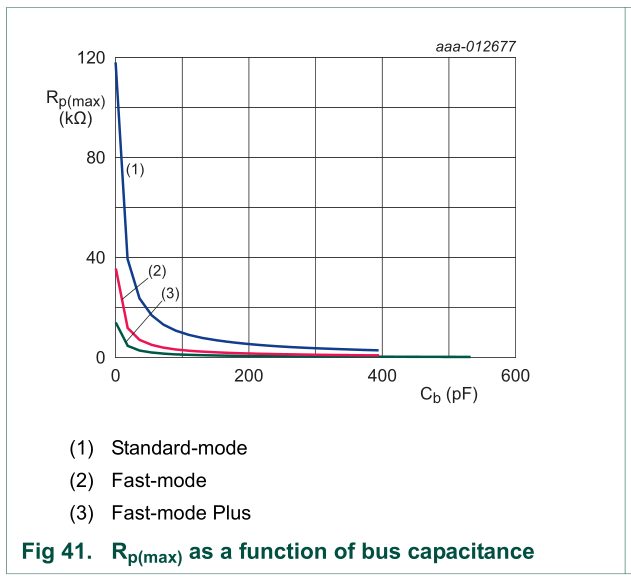

最大电阻 Rp 和总线电容 Cb 关系图:

note:建议总线电容维持在 100pF 以下。

关于 I2C 的方方面面,我写在了我的博客上,有 10 篇,包括 I2C 的传输协议和Linux 下 I2C 的软件驱动框架,大家可以去查看,网址如下:

http://www.linuxer.vip/i2c-bus-spec/

也可以在左下角点击阅读原文,电脑端阅读更方便。

·················· END ··················

点击关注公众号,免费领学习资料