苹果A17预定首发!台积电宣布2023年投产增强版3nm Plus工艺

新智元报道

新智元报道

来源:外媒

编辑:Q

【新智元导读】台积电宣布,将会在 2023 年推出 3nm 工艺的增强版,命名为「3nm Plus」,首发客户是苹果。如果苹果继续一年一代芯片,那么到 2023 年使用 3nm Plus 工艺的,将会是苹果「A17」。

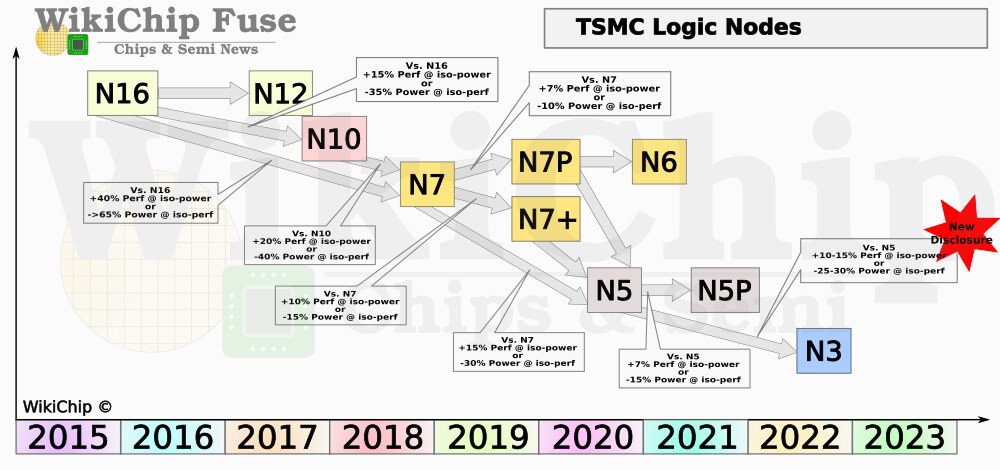

苹果 A14,三星 Exynos 1080,麒麟9000,Snapdragon 888等芯片都使用了5nm技术,在这方面,台积电和三星各占一半。根据目前的路线图,5nm技术将在明年进行小幅升级。所以3nm技术,真正作为一个迭代恒等式出现,需要等到2022年。

继台积电2022年3nm 的大规模生产计划公布后,外媒报道台积电计划在2023年开始3nm Plus 增强版的生产。毫无疑问,苹果仍将首发。

如无意外,3nm Plus将在iPhone15上的A17处理器首发

如果苹果的命名规则保持不变,那么2023年相应的 A17处理器应该用在 iPhone 15上。当然,Mac 上的 M 系列处理器肯定也会被使用。到那时,苹果或许将不再拥有带有英特尔处理器的 Mac 产品。

根据之前的报道,3nm 将实现15% 的性能改进,30% 的功耗降低和70% 的晶体管密度增加。但是3nm Plus 的具体参数还不清楚。

虽然台积电没有透露 3nm Plus 相比于 3nm 有何变化,但是显然会有更高的晶体管密度、更低的功耗、更高的运行频率。

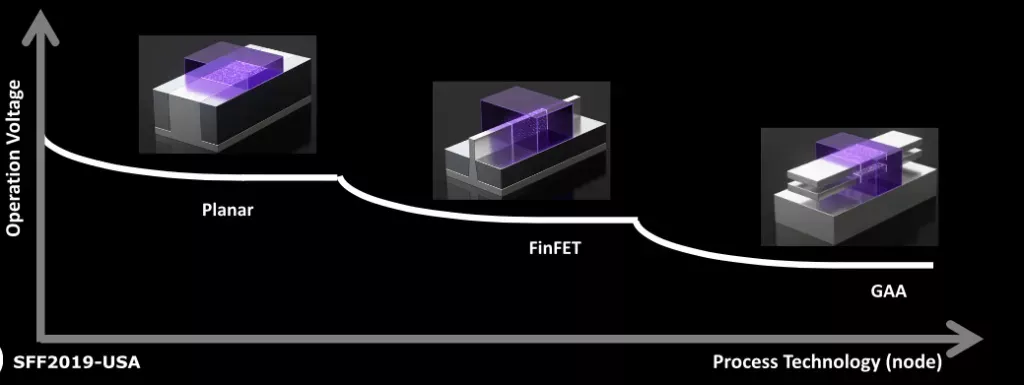

技术方面,台积电的3nm 仍然使用 FinFET 鳍型场效应晶体管,而三星的3nm 使用更先进的 GAA 环绕栅晶体管方法。

在这方面,台积电认为,目前的 FinFET 工艺拥有更好的成本和能耗效率。因此,第一批3nm芯片仍将使用 FinFET 晶体管技术。然而,台积电的老对手三星正押注于3nm节点的上市,它的进步和技术选择是非常激进的,将抛弃 FinFET 晶体管,直接使用 GAA 包围栅晶体管。

早在今年4月,台积电就公布了一些3nm工艺技术细节。它的晶体管密度创造了一个新的记录,达到2.5亿/mm2。作为对比,麒麟9905G 与 TSMC 的7nm EUV 工艺有一个尺寸为113.31mm2,晶体管密度为103亿,平均9000万/mm2。然而,3nm工艺晶体管密度是7nm工艺的3.6倍。这种密度在视觉上类似于将奔腾4处理器缩小到针的大小。

3nm工艺:2022年量产,苹果A16芯片将首发

台积电为3nm工艺一共准备了4波产能,其中首波产能中的大部分,将留给他们多年的大客户苹果,后三波产能将被高通英伟达等厂商预订。

N3 的制作方法采用 FinFET 晶体管结构,适用于移动和高性能计算应用。

台积电曾表示,3nm沿用 FinEFT 技术,主要是考量客户在导入5nm制程的设计也能用在3nm制程中,无需面临需要重新设计产品的问题,台积电可以保持自身的成本竞争力,获得更多的客户订单。据悉这个新节点使用极紫外辐射光刻技术(EUVL)进行多达20多层的光刻,这是目前没有新工艺能做到的。

在更遥远的2nm工艺上,台积电将放弃多年的FinFET(鳍式场效应晶体管),甚至不使用三星规划在3nm工艺上使用的 GAAFET (环绕栅极场效应晶体管),也就是纳米线(nanowire),而是将其拓展成为 MBCFET(多桥通道场效应晶体管),也就是纳米片(nanosheet)。

FinFET能力探底,新技术散热问题没有解决

晶体管是芯片中的关键构建模块之一,可在设备中提供开关功能。市场预测5nm的命运可能步10nm后尘,成为从6nm到3nm的过渡。

随着芯片转向3nm及更先进的制程,FinFET能力已经探底,部分代工厂希望在2022年迁移到称为纳米片FET的下一代晶体管。纳米片FET属于所谓的gate-all-around FET。

纳米片FET是FinFET的扩展。它的侧面是FinFET,栅极包裹着它。纳米片将出现在3nm处,并可能延伸至2nm甚至1nm。

还有其他gate-all-around类别,例如,Imec正在开发2nm的forksheet FET、Complementary FET (CFET)。

在forksheet FET中,nFET和pFET都集成在同一结构中,具有42nm的接触栅间距(CPP)和16nm的金属间距,允许更紧密的n到p间距并减少面积缩放。

CFET由两个单独的纳米线FET(p型和n型)组成。Imec的董事介绍,CFET通过“折叠”pFET器件上的nFET将电池有效面积减小了两倍,但是散热成了问题。

光刻技术是在芯片上构图微细图形的技术,有助于实现芯片缩放。但是在5nm工艺下,当前的基于光学的193nm光刻扫描仪已经尽力了。

在3nm及以上的工艺中,芯片制造商可能需要一种称为高数值孔径EUV(high-NA EUV)的EUV光刻新技术。芯片商希望这种既复杂又昂贵的技术能够在2023年研制成功。

纵观全球半导体制程玩家,目前仅剩三足鼎立:英特尔、三星和台积电。而其中真正卯着劲在攻坚3nm的,其实只有三星和台积电两家而已,3年后是怎样的结局,让我们拭目以待。