从苹果 M1 到英伟达 Grace,“缝合风”为何在芯片大厂中盛行?

👇👇关注后回复 “进群” ,拉你进程序员交流群👇👇

作者 | 马超

出品 | CSDN(ID:CSDNnews)

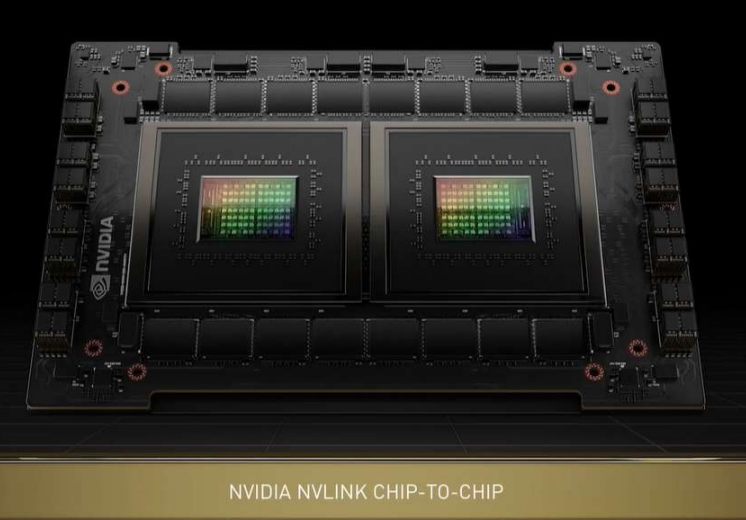

历史不会简单重复,但总是惊人的相似。之前在电影、游戏等人文领域流行的缝合风,似乎也对IT界芯片设计师们产生了影响。在英伟达最新的发布会上,黄仁勋发布的Grace CPU Superchip,其实就是用两块Grace CPU粘在一起而形成的炸裂之作。

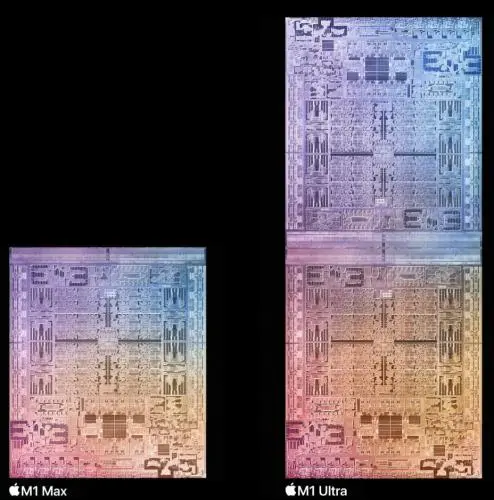

而苹果春晚上发布的M1 Ultra也是同样的配方,同一个套路,他们直接把两块M1 Max拼到一块,就这样一款新的“伟大”芯片就诞生了。

当然笔者这里对于此类缝合作品并不抱有偏见,毕竟像“原神”那样的作品在上市之初也被指责是缝合怪,但这丝毫不影响米哈游目前的大杀四方,让来自于各个国家的粉丝都疯狂氪金,不过这种缝合式芯片的大行其道,其实是缺芯潮不断持续而产生的影响,由于科技业界忙于眼前的苟且,创新后劲不足,对新设计、新理念缺乏信心,在这种情况下考虑到原来的M1 Max已经大获成功了,而且台积电的制造经验也成熟,把两块已经成熟的芯片粘在一起,风险要远比造全新的芯片要小得多。

其实这股缝合风从苹果的初代M1就开始了,只是初代的M1目标是把CPU、GPU、内存缝合到一起,由于使用的都是片内内存,所以理论上讲M1系列的全族芯片都不支持内存扩展,要换只能把CPU、GPU打包一起换掉。当然缝合方案的影响不止于此,下面我们就来分析一下这种芯片缝合方案的具体情况。

内存带宽极高,CPU和GPU通信能力超强

由于内存完全被芯片集成,内存与CPU之间的通信也就不用经过主板进行转手了,因此目前我们可以看到英伟达的Grace CPU的内存带宽可以达到惊人每秒1TB,而苹果M1 Ultra也是不遑多让,有每秒800GB的成绩。这是我们一般主板接入内存的普通X86玩家所不能想象的效果,可见甩了主板这个中间商以后,其实内存的速度还是能打的。

另外由于M1系列缝合式芯片内存、GPU都是由CPU进行统一管理,也就是说内存与显存是共享的,这就可以大大提高CPU与GPU的通信效率,从而增强图像处理、3D建模等任务的处理效率。由于英伟达Grace尚未投产,具体细节还不多,因此这里这种片内共享所带来的加成效应,我们继续以苹果M1举例,苹果初代M1显存与内存加在一起只有16G,而M1前一代的Mac Pro内存是128G,光是显存都有与M1持平16G,不过搭载M1的入门版Mac在进行图像处理等任务时,却要比上一代顶配的Mac还要强出近一倍。而本次发布的M1 Max更是直接将内存带宽提升到初代M1的6位,其性能加强的程度也就可想而知了。

英伟达最近发布处理器中用到的缝合技术NVlink,其实采用了和苹果比较类似的思路。未来不排除英特尔和AMD也会跟进,今后内存也很可能不会再是一个单独的元件了,被集成起来也会是一种趋势。

AI算力史诗级提升,元宇宙可期

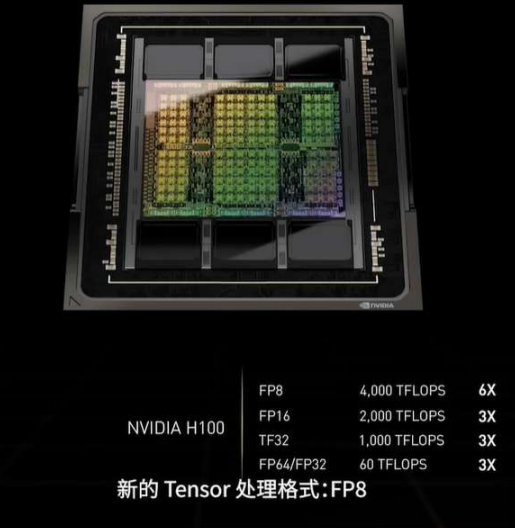

在AI优化方面,现在看来未来主流的Tensor也就是矢量的主流格式正在由FP32向FP8。在英伟达最新的显卡H100中,主打的矢量格式就已经明确是FP8了。

不管是AI计算,还是元宇宙概念,其最基本的计算单元都是矢量。以深度神经网络为例,神经元可以抽象为对于输入矢量乘以权重以表示信号强度乘积加总,再由ReLU、Sigmoid等应用激活函数调节,本质是将输入数据与权重矩阵相乘,并输入激活函数,对于有三个输入数据和两个全连接神经元的单层神经网络而言,需要把输入和权重进行六次相乘,经典CNN中无论GEMM的矩阵乘法运算还是卷积地乘加计算都是使用FP32也就是用32位字长的数字来表示的,在这种情况下如果我们可以使用FP8来作为输入表示此以过程,其计算量至少可以下降75%。尤其在图像处理的场景下,通常由FP32到FP8的转换,如果方案得当,其精度损失是低于1%的。因此在针对FP8类型的计算加速也就是业界都在探讨的话题。

由于之前英特尔去年至强三代中引入的VNNI已经针对FP8进行过加速优化,据笔者所知咱们国内某大厂在实时生成用户3D头像模型的应用中,在VNNI的支持下可以在精度降低1%的情况下,性能还提升了4.23倍。而这次英伟达的发布会上,黄仁勋的说法也为FP8投上了关键一票。

RISC的自带光环,超强的译码器

目前处理器的流水线一般分为取指、译码、取操作数等等环节,其中译码是一个非常重要的环节。译码器方面ARM架构的精简指令集的确有一定优势,由于指令都是定长的,完全可以做出高效的多路译码器以提升效率。据笔者所知之前初代M1应该是四路译码,目前的M1 MAX和Ultra都是6路指令解码器,8µop发射宽度,6路分配、10路执行端口的指标。但是英特尔和AMD想用缝合方案的话,就需要实现像M1 Ultra这么强的译码器,但由于X86指令集是变长的,因此X86芯片的译码器一般都先按短码进行翻译,遇差错再返工,这也就很难在相同的功耗下达到很强的译码效率。

未来趋势-打破指令集之间的墙

在英特尔IDM 2.0的战略当中有一个重要原则,那就是敞开大门,全面接收各种芯片的订单,同时也可以考虑在同一芯片中集成多种不同指令集的核心,这可能终极的缝合目标,也就是同一块芯片中可以由英特尔的CPU当大核,ARM的CPU当小核,AMD的显卡当GPU的神奇组合。

这种趋势在英特尔去年发布的Alder Lake处理器中搭建的Thread Director上已经显出端倪。Thread Director就是这样一种软、硬结合的核心调度方案,英特尔的做法是在处理器中集成了一个专用的MCU,用来监控当前处理器内核的运行情况,能够监测到每个线程的特征,比如它运行什么样的指令集、它的性能需求如何等等。在收集完信息之后,MCU会将收集到的信息反馈给操作系统,再次操作系统把这些信息与线程调度信息相结合,判断是否应该将线程转移到别的核心上。如果与操作系统结合的好话,那么一轮调度信息采集工作仅需要30微秒就能完成,而传统方案调度器可能需要100多毫秒才能判断出结论。据了解,Alder Lake上集成的这颗调度用的MCU就是RISC-V的核心,一切就是这么奇妙。

天下大势合久必分,分久必合,因此缝合芯片,也符合现在芯片行业的发展趋势,不过这种缝合这款处理器如何在虚拟化的云环境中,为不同用户提供服务,并进行严格的隔离可能也是一个难点,但是可以肯定的是英伟达、英特尔和苹果的接连站台,缝合式芯片的未来可期。

-End-

最近有一些小伙伴,让我帮忙找一些 面试题 资料,于是我翻遍了收藏的 5T 资料后,汇总整理出来,可以说是程序员面试必备!所有资料都整理到网盘了,欢迎下载!

点击👆卡片,关注后回复【

面试题】即可获取