DDR内存中的纠错码 (ECC)

简介

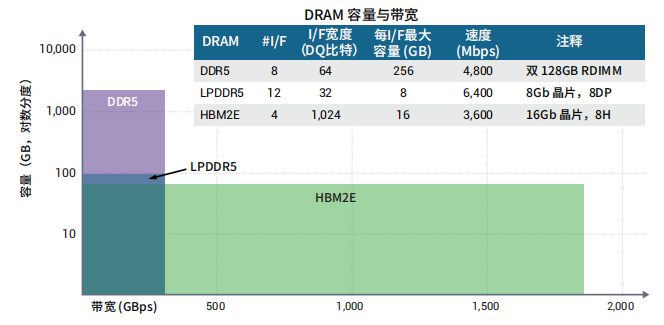

双倍数据速率同步动态随机存取内存(DDR SDRAM 或简称 DRAM)技术如今已成为几乎所有应用的主内存,无论是在高性能计算 (HPC) ,还是在注重功耗、面积的移动应用中。这要归功于 DDR 的诸多优势,包括高密度、简单架构、低延迟和低功耗。作为规定内存标准的标准组织,JEDEC 定义并发展了四个 DRAM 类别,用于指导设计人员准确满足其内存要求:标准 DDR (DDR5/4/3/2)、移动 DDR (LPDDR5/4/3/2)、图形 DDR (GDDR3/4/5/6) 和高带宽 DRAM (HBM2/2E/3)。

图 1 显示了典型的片上系统 (SoC) 中的内存子系统的结构图,该内存子系统包括 DDR 内存控制器、DDR PHY、DDR 信道和 DDR 内存。根据 JEDEC 的定义,DDR 信道由命令/地址和数据通道组成。以下显示的简化 DDR 内存可以代表上述四类中任何一类的 DRAM 内存组件。

图 1:SoC 中的内存子系统框图

作为内存 RAS 功能的 ECC

ECC 数据由控制器根据实际的 WR(写入)数据生成。内存同时存储写命令的数据和 ECC 数据。 在 RD(读取)操作期间,控制器从内存读取数据和相应的 ECC 数据。控制器利用接收到的数据重新生成 ECC 数据,并将其与接收到的 ECC 数据进行比较。 如果两者匹配,则不会发生错误。如果不匹配,ECC SECDED 机制允许控制器纠正任何单 bit 错误并检测双 bit 错误。

ECC 方案

结语

纠错码 (ECC) 方案是一种获得广泛使用的内存 RAS 功能。使用标准 DDR 内存的应用通常实现 side-band ECC,而使用 LPDDR 内存的应用则实现 inline ECC。DDR5 和 LPDDR5 信道具有更高的速度,因此 SI 效应很明显,现在,甚至 DDR5 和 LPDDR5 DRAM 也分别支持 on-die ECC 和 link ECC。新思科技的 DesignWare® DDR5/4 和 LPDDR5/4 IP 解决方案提供先进的 RAS 功能,包括本文重点介绍的所有 ECC 方案。

推荐阅读:

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

推荐阅读

更多架构相关技术知识总结请参考“架构师技术全联盟书店”相关电子书(35本技术资料打包汇总详情可通过“阅读原文”获取)。

全店内容持续更新,现下单“架构师技术全店打包汇总(全)”,后续可享全店内容更新“免费”赠阅,价格仅收188元(原总价290元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“架构师技术全店资料打包汇总(全)”电子书资料详情。