收藏: 全面解析FPGA基础知识

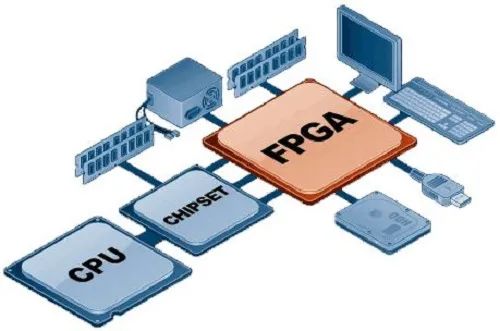

FPGA (Field Programmable Gate Array)即现场可编程门阵列。它是在PLA、PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

1、 FPGA简介

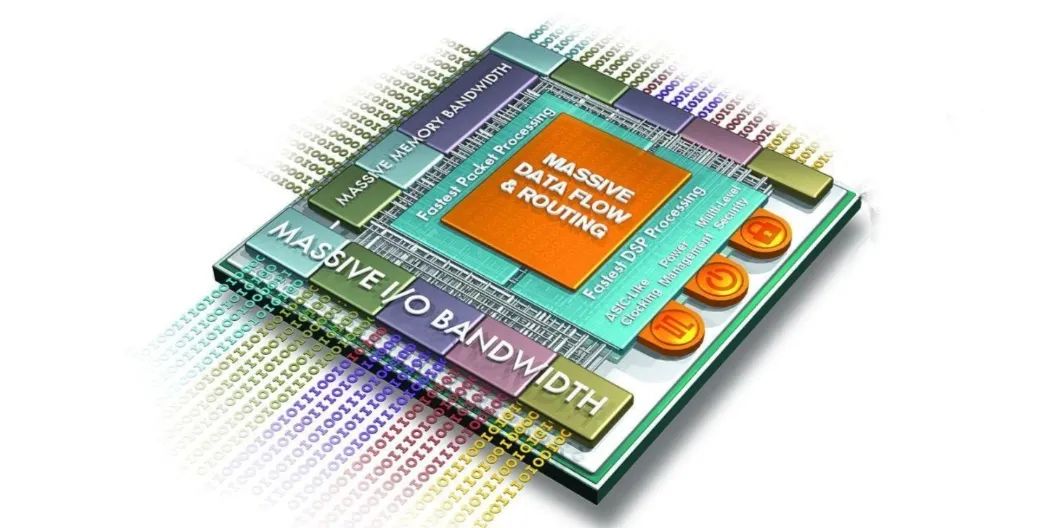

FPGA普遍用于实现数字电路模块,用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的需求。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。可以毫不夸张的讲,FPGA能完成任何数字器件的功能,下至简单的74电路,上至高性能CPU,都可以用FPGA来实现。FPGA如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。

2、FPGA发展史

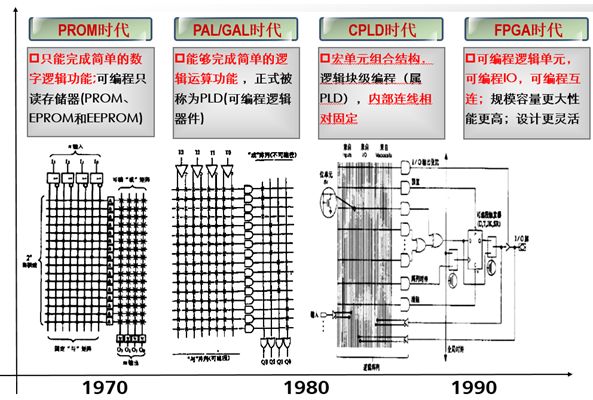

FPGA的发展历史如下图所示。相对于PROM、PAL/GAL、CPLD而言,FPGA规模更大性能更高。

图1 FPGA发展史

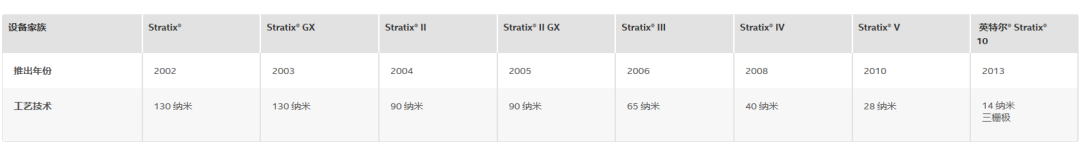

FPGA芯片主流生产厂家包括Xilinx、Altera、Lattice、Microsemi,其中前两家的市场份额合计达到88%。目前FPGA主流厂商全部为美国厂商。国产FPGA由于研发起步较美国晚至少20年,目前还处于成长期,仅限于低端,在通信市场还没有成熟应用。

2015年12月,Intel公司斥资167亿美元收购了Altera公司。Altera被收购后不久即制定了英特尔处理器与FPGA集成的产品路线图。这两种产品集成的好处是可以提供创新的异构多核架构,适应例如人工智能等新市场的需求,同时能大幅缩减功耗。

图2 FPGA在电信领域的应用历史

FPGA在航天、军工、电信领域有非常成熟和广泛的应用。以电信领域为例,在电信设备一体机阶段,FPGA由于其编程的灵活性以及高性能被应用网络协议解析以及接口转换。

在NFV(NetworkFunction Virtualization阶段,FPGA基于通用服务器和Hypervisor实现网元数据面5倍的性能提升,同时能够被通用Openstack框架管理编排。

在云时代,FPGA已经被作为基本IaaS资源在公有云提供开发服务和加速服务,AWS、华为、BAT均有类似通用服务提供。

截至目前,Intel的Stratix 10器件已被成功应用于微软实时人工智能云平台Brainwave项目。

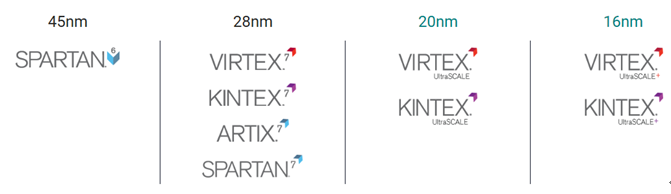

3、两家主流FPGA公司发展近况

Xilinx聚焦芯片领先和丰富的加速解决方案,通过开放策略获得主流云平台支持,确立了其在数据中心的领先地位。其UltraScale+系列FPGA领先友商1年多,使其在云平台竞争中占领先机,其VU9P器件被大量应用于包括AWS、Baidu、Ali、Tencent及华为在内的多家公司的云计算平台。

为满足加速器领域对FPGA芯片日益递增的性能需求,Xilinx已发布面向数据中心的下一代ACAP芯片架构、推出7nm Everest器件。此器件已不属于传统的FPGA,它集成了ARM、DSP、Math Engine处理器阵列等内核,将于2019年量产。相较于VU9P,Everest支持的AI处理性能将能提升20倍。

Intel则提供从硬件到平台到应用的全栈解决方案,不开放硬件和平台设计以避免生态碎片化,投入巨大但进展缓慢。

图3 Xilinx产品系列图

图4 Intel(以Stratix系列为例)产品工艺年代

FPGA在数据中心服务器市场的实际应用中存在一定技术难点,具体包括如下几方面:

1、编程门槛较高:硬件描述语言不同于软件开发语言,需要开发者对底层硬件有着较深刻的认识;因此人才也就成为限制FPGA应用的一个重要因素。据了解,目前国内从事FPGA开发的人员初步估计大约两万多人。

2、集成难度较大:FPGA开发与应用需要软硬件的协同,包括使用高级语言的系统建模、硬件代码(电路)设计、硬件代码仿真、底层驱动软件与硬件逻辑的联调等等。

3、开发周期相对软件要长:硬件开发比软件开发过程复杂,调试周期也被拉长。

4、很难获取独立逻辑IP。

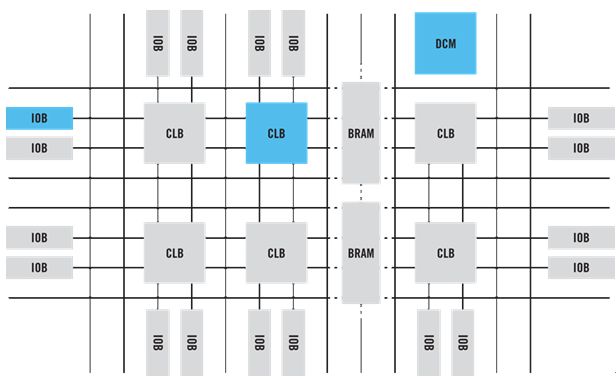

4、FPGA整体结构

FPGA架构主要包括可配置逻辑块CLB(Configurable Logic Block)、输入输出块IOB(Input Output Block)、内部连线(Interconnect)和其它内嵌单元四个部分。

CLB是FPGA的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个CLB都包含一个由4或6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

FPGA可支持许多种I/O标准,因而可以为系统设计提供理想的接口桥接。FPGA 内的I/O按bank分组,每个bank能独立支持不同的I/O标准。目前最先进的FPGA提供了十多个I/O bank,能够提供灵活的I/O支持。

CLB 提供了逻辑性能,灵活的互连布线则负责在CLB和I/O之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低skew布线(全局性专用布线资源)。一般,各厂家设计软件会将互连布线任务隐藏起来,用户根本看不到,从而大幅降低了设计复杂性。

内嵌硬核单元包括RAM、DSP、DCM(数字时钟管理模块)及其它特定接口硬核等,FPGA器件内部结构如下示意图。

图5 FPGA器件内部结构图

一般来说,器件型号数字越大,表示器件能提供的逻辑资源规模越大。在FPGA器件选型时,用户需要对照此表格,根据业务对逻辑资源(CLB)、内部BlockRAM、接口(高速Serdes对数)、数字信号处理(DSP硬核数)以及今后扩展等多方面的需求,综合考虑项目最合适的逻辑器件。

5、FPGA开发流程

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的开发流程一般如下图所示,包括功能定义/器件选型、设计输入、功能仿真、逻辑综合、布局布线与实现、编程调试等主要步骤。

1、功能定义/器件选型:在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。

2、 设计输入:设计输入指使用硬件描述语言将所设计的系统或电路用代码表述出来。最常用的硬件描述语言是Verilog HDL。

3、 功能仿真:功能仿真指在逻辑综合之前对用户所设计的电路进行逻辑功能验证。仿真前,需要搭建好测试平台并准备好测试激励,仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用仿真工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS等软件。

4、 逻辑综合:所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。为了能转换成标准的门级结构网表,HDL程序的编写必须符合特定综合器所要求的风格。常用的综合工具有Synplicity公司的Synplify/Synplify Pro软件以及各个FPGA厂家自己推出的综合开发工具。

5、布局布线与实现:布局布线可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告);实现是将综合生成的逻辑网表配置到具体的FPGA芯片上。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

6、编程调试:设计的最后一步就是编程调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generaon),将编程数据加载到FPGA芯片中;之后便可进行上板测试。最后将FPGA文件(如.bit文件)从电脑下载到单板上的FPGA芯片中。

6、如何使用FPGA

FPGA开发完毕,最终得到验证好的加载文件。输出加载文件后,即可开始正常业务处理和验证(以软件加载方式为例,描述整个过程)

1、逻辑加载;

2、单板软件加载逻辑后,需要复位逻辑;

3、复位完成后,软件需等待等待一段时间至逻辑锁相环工作稳定;

4、软件启动对逻辑的外部RAM、内部Block RAM、DDRC等的自检操作;

5、软件完成自检以后,对逻辑所有可写RAM空间及寄存器进行初始化操作;

6、初始化完毕,软件参考逻辑芯片手册配置表项及寄存器;

7、逻辑准备好,可以开始处理业务。

7、FPGA适用场景

FPGA适合非规则性多并发、密集计算及协议解析处理场景,例如人工智能、基因测序、视频编码、数据压缩、图片处理、网络处理等各领域的加速。

转载申明:转载本号文章请注明作者和来源,本号发布文章若存在版权等问题,请留言联系处理,谢谢。

推荐阅读

更多架构相关技术知识总结请参考“架构师技术全联盟书店”相关电子书(35本技术资料打包汇总详情可通过“阅读原文”获取)。

全店内容持续更新,现下单“架构师技术全店打包汇总(全)”,后续可享全店内容更新“免费”赠阅,价格仅收188元(原总价290元)。

温馨提示:

扫描二维码关注公众号,点击阅读原文链接获取“架构师技术全店资料打包汇总(全)”电子书资料详情。