5nm芯片为何集体翻车?10年前困扰台积电三星的问题又回来了

来源:魔铁的世界

作者:魔铁

物联网智库 转载

二次转载请联系原作者

导 读

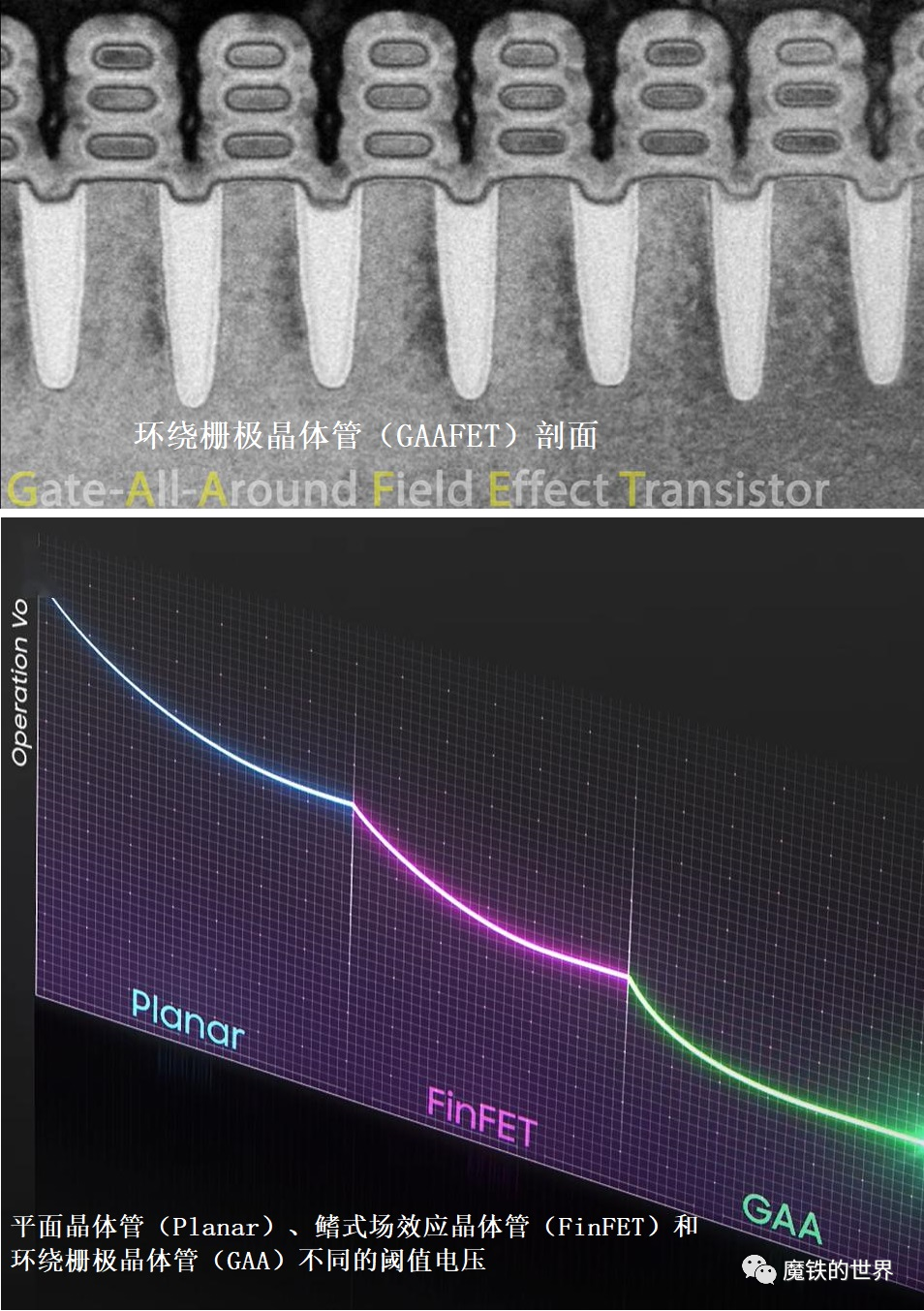

在环绕栅极晶体管(GAAFET)正式撸起袖子上阵之前,芯片的发热仍然会是一个问题。

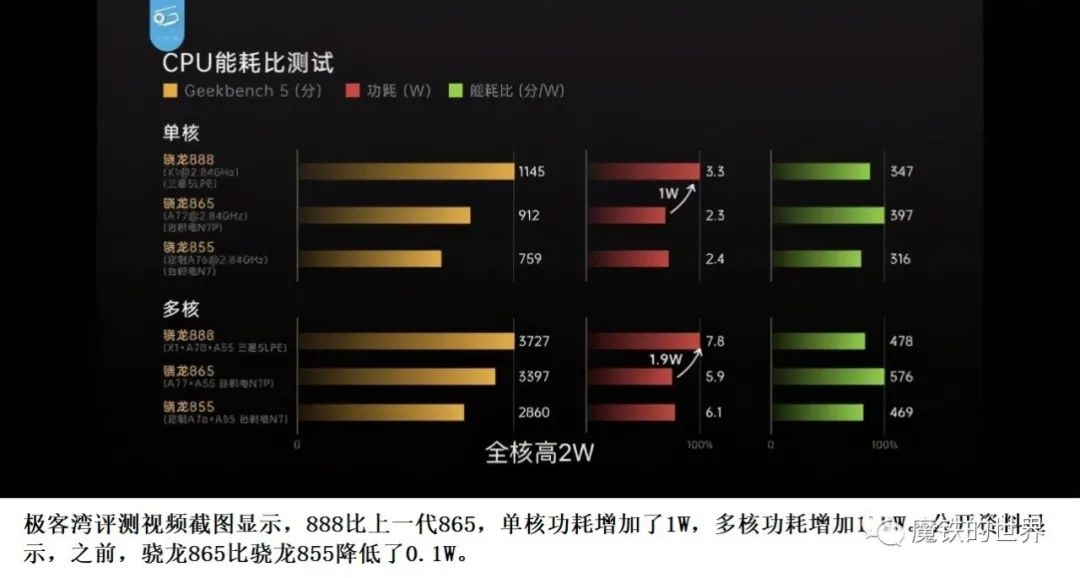

骁龙888功耗等于低压酷睿?

为何晶体管漏电是元凶?

台积电为何被称台漏电?

为何老迈的技术不退休?

版权声明:“物联网智库”除发布原创干货以外,致力于优秀科技/研究/投资类文章精选、精读。部分文章推送时未能与原作者取得联系。若涉及版权问题,或由于二次转载标错了转载来源,敬请原作者联系我们。联系方式:微信Sun_moon_salvation

往期精选

评论