数字电路电平标准全解析

本文来源:EDN电子技术设计

聊一聊现有电脑扩展串口和并口的问题(认知神经科学实验需求,含台式机和笔记本)

并口与串口的区别

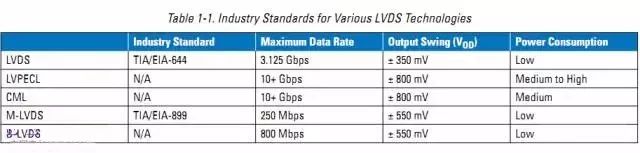

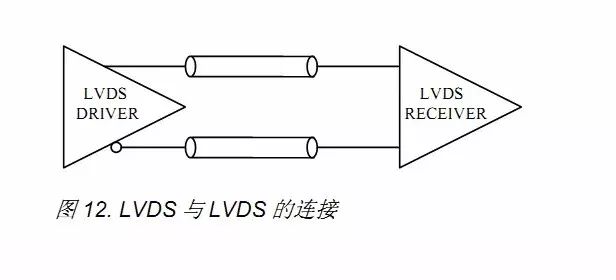

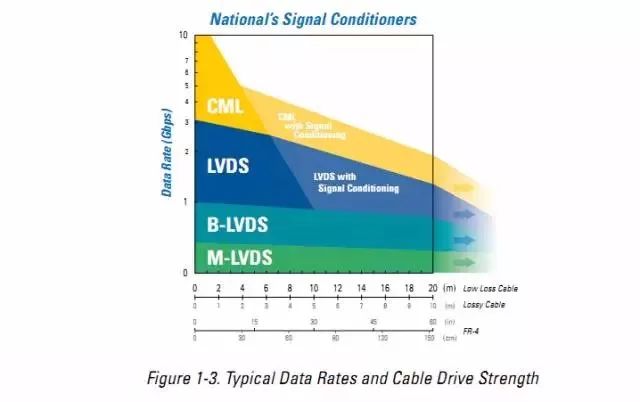

LVDS的连接方式:直接连接,因为片内具有端接电阻。

LVDS的连接方式:直接连接,因为片内具有端接电阻。

谢谢大家观看,如有帮助,来个喜欢或者关注吧!

博客网址:https://7988888.xyz/

知乎网址:https://www.zhihu.com/people/braintechnology

知识星球 : https://t.zsxq.com/aeimaqv

本文内容参考以上网址。以上内容仅供学习使用,不作其它用途,如有侵权,请留言联系,作删除处理!

有任何疑问及建议,扫描以下公众号二维码添加交流:

评论